## Fault Attacks

Side-Channel Security

## Rishub Nagpal

June 13, 2024

IAIK - Graz University of Technology

If you found (parts) of this lecture interesting, consider doing a master project/thesis with us!

Some topics I offer:

- Single-Trace Side Channel Attacks (Like task 2, but more detail)

- Masking Countermeasures for Software and Hardware

- Machine Learning for SCA

- Implementing SCA tools efficiently in Rust

- Attacking Post-Quantum crypto on real devices

Recap

Differential Fault Attacks

Statistical Fault Attacks

Countermeasures

Breaking Countermeasures Again

## Recap

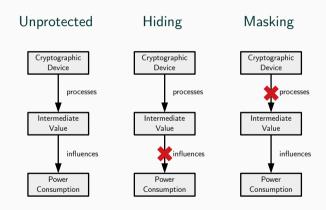

- Power analysis attacks

- Countermeasures

- Hiding (Shuffling)

- Masking

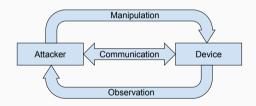

- Attacker has (legitimate) access to device

- Thus far: Passive attacks (and countermeasures)

- But the attacker can do much more...

- Induce fault in computation: Erroneous result

- Transient faults: Only current computation (gone after reset, at the latest)

- Induce fault in computation: Erroneous result

- Transient faults: Only current computation (gone after reset, at the latest)

- Fault injection techniques

- Spike/glitch attacks (clock, Vdd, IO, ...)

- Laser, BBI

- Rowhammer, Plundervolt

- ...

- Induce fault in computation: Erroneous result

- Transient faults: Only current computation (gone after reset, at the latest)

- Fault injection techniques

- Spike/glitch attacks (clock, Vdd, IO, ...)

- Laser, BBI

- Rowhammer, Plundervolt

- ...

- Effects

- Instruction skip

- Data corruption

- ...

Remember?

- PayTV (early 2000s)

- Pirated cards bricked via remote firmware update

- Inserted infinite loop, otherwise unchanged

- Solution: Glitching! Increment IP, but no jmp

- "Unlooper" device

```

// startup loop:

jmp loop;

// continue to bootloader

```

Remember?

- PayTV (early 2000s)

- Pirated cards bricked via remote firmware update

- Inserted infinite loop, otherwise unchanged

- Solution: Glitching! Increment IP, but no jmp

- "Unlooper" device

- Gaming devices

- Xbox360 reset hack

- Voltage glitching on reset line

- Execute untrusted code (modified firmware)

```

// startup loop:

jmp loop;

// continue to bootloader

```

- Attack cryptographic implementations

- We want to get the key

- Fault injection alone (mostly) does not leak the key

- → More work is needed

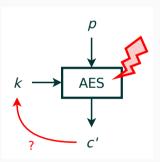

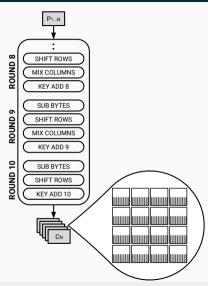

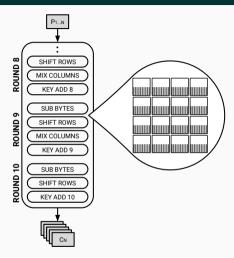

**Differential Fault Attacks**

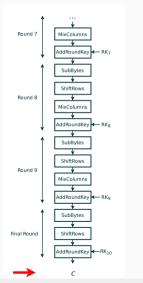

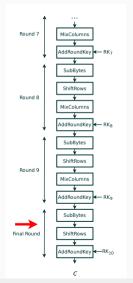

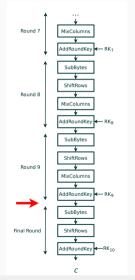

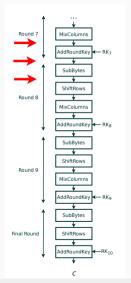

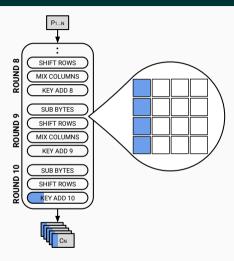

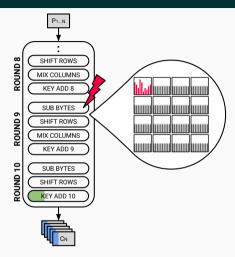

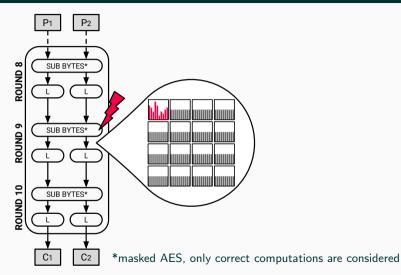

- Inject fault during AES encryption

- Get: Faulty ciphertext c'

- Want: Key

- ullet  $\to$  Faulting alone is only half the game!

- Inject fault during AES encryption

- Get: Faulty ciphertext c'

- Want: Key

- ullet  $\to$  Faulting alone is only half the game!

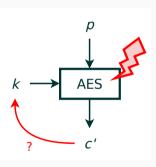

- Idea: Compare correct and faulty ciphertext

- Encrypt same plaintext twice, once with a fault

- Use difference in ciphertext to recover the key

- → Differential Fault Attack

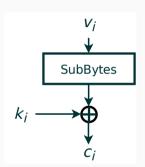

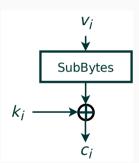

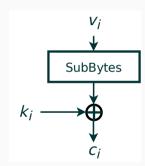

- Pick an intermediate v

- *v* is combined with a small part of the last round key

- Pick an intermediate v

- v is combined with a small part of the last round key

- 2 invocations with same p, once with fault in v

- Usually we don't know exact effect

- Could be flipping 1 bit/byte

- Could be randomization of 1 bit/byte

- Enumerate possible subkey values

- Compute backwards for each guess

- Check if XOR-difference = fault model

- ullet Wrong guess: "randomized" v and  $\Delta v$

- Enumerate possible subkey values

- Compute backwards for each guess

- Check if XOR-difference = fault model

- ullet Wrong guess: "randomized" v and  $\Delta v$

- Remember: AES key schedule is invertible

- If it were not: Attack decryption or attack round after round

• Faulting Ciphertext?

- Faulting Ciphertext?

- No!

- Faulting Ciphertext?

- No!

- ullet  $\Delta c$  does not depend on a key

- Faulting before AddRoundKey10?

- ... depends on type of fault

- Faulting before AddRoundKey10?

- ... depends on type of fault

- Fault model 1: Stuck-at known (can set v to a specific value)

- Attack possible!

- Example: v stuck at  $0 \rightarrow c = v \oplus k = k$

- Faulting before AddRoundKey10?

- ... depends on type of fault

- Fault model 1: Stuck-at known (can set v to a specific value)

- Attack possible!

- Example: v stuck at  $0 \rightarrow c = v \oplus k = k$

- Problem: Stuck-at-known hard to do (reliably)

- Easier: Random flips, stuck-at-unknown, ...

- Faulting before AddRoundKey10?

- ... depends on type of fault

- Faulting before AddRoundKey10?

- ... depends on type of fault

- Fault model 2: Random flips

- Faulting before AddRoundKey10?

- ... depends on type of fault

- Fault model 2: Random flips

- No attack possible!

- Fault propagates through XOR  $\rightarrow$   $\Delta c$  does not depend on the key  $c = v \oplus k$   $c' = (v \oplus \Delta v) \oplus k = c \oplus \Delta v$

• Faulting before ShiftRows10?

- Faulting before ShiftRows10?

- Same situation as for AddRoundKey

- Attack possible

- ShiftRows just rearranges bytes

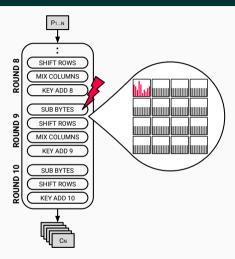

- Faulting before SubBytes10?

- ... depends on fault type

- Faulting before SubBytes10?

- ... depends on fault type

- Fault Model 1: Flip 1 bit

- Attack possible

- ... but hard to achieve single flipping bit (precise Laser)

• Correct output = 1a, faulty output = 99

$k = 0 \quad 1 \quad 2 \quad 3 \quad 4 \quad 5 \quad 6 \quad 7 \quad 8 \dots$

C = 1a : S^-1(C xor k):

$C' = 99 : S^{-1}(C' \text{ xor } k):$

• Correct output = 1a, faulty output = 99

```

k = 0 1 2 3 4 5 6 7 8 ...

C = 1a : S^-1(C xor k): 43 44 34 8e e9 cb c4 de 39 ...

C' = 99 : S^-1(C' xor k): f9 e2 e8 37 75 1c 6e df ac ...

```

• Only few keys have this property: Filter them!

Correct output = 1a, faulty output = 99

```

C = 1a : S^-1(C xor k): 43 44 34 8e e9 cb c4 de 39 ...

C' = 99 : S^-1(C' xor k): f9 e2 e8 37 75 1c 6e df ac ...

```

$k = 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \dots$

- Only few keys have this property: Filter them!

- Use another c/c' pair to get down to 1 key

- Faulting before SubBytes10?

- ... depends on fault type

- Fault Model 2: Random byte fault (unknown)

- Faulting before SubBytes10?

- ... depends on fault type

- Fault Model 2: Random byte fault (unknown)

- Much easier to achieve (on an 8-bit implementation)

- ullet ... but no attack possible

• Faulting before AddRoundKey9?

- Faulting before AddRoundKey9?

- Important observation:  $\Delta v = v \oplus v' = (v \oplus k) \oplus (v' \oplus k)$

- Faulting before AddRoundKey9?

- Attack possible

- $\bullet$  Exactly the same as previously (RK9 cancels out)

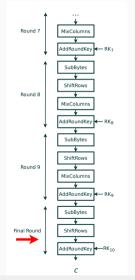

• Faulting before MixColumns9?

- Faulting before MixColumns9?

- Fault Model: Random byte fault (unknown)

- Attack possible!

- Comparably easy to achieve

- Basis for Piret's attack

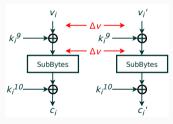

$\bullet$  Model byte fault using (unknown) difference  $\Delta\colon\thinspace \nu_1'=\nu_1\oplus\Delta$

## **Fault Propagation of MixColumns**

- $\bullet$  Model byte fault using (unknown) difference  $\Delta\colon\thinspace \nu_1'=\nu_1\oplus\Delta$

- MixColumns: Linear operation, 4 byte input: MixColumns( $[v_1 \oplus \Delta, v_2, v_3, v_4]$ ) = MixColumns( $[v_1, v_2, v_3, v_4]$ )  $\oplus$  MixColumns( $[\Delta, 0, 0, 0]$ )

#### Fault Propagation of MixColumns

- • Model byte fault using (unknown) difference  $\Delta\colon\thinspace \nu_1'=\nu_1\oplus\Delta$

- MixColumns: Linear operation, 4 byte input: MixColumns( $[v_1 \oplus \Delta, v_2, v_3, v_4]$ ) = MixColumns( $[v_1 \quad , v_2, v_3, v_4]$ )  $\oplus$  MixColumns( $[\Delta, 0, 0, 0]$ )

- Observe: 4 byte input, but only 1 is active in  $MixColumns([\Delta, 0, 0, 0])$

- Only 255 possible MixColumns outputs!

- Model byte fault using (unknown) difference  $\Delta \colon \mathit{v}_1' = \mathit{v}_1 \oplus \Delta$

- MixColumns: Linear operation, 4 byte input: MixColumns( $[v_1 \oplus \Delta, v_2, v_3, v_4]$ ) = MixColumns( $[v_1 \quad , v_2, v_3, v_4]$ )  $\oplus$  MixColumns( $[\Delta, 0, 0, 0]$ )

- Observe: 4 byte input, but only 1 is active in  $MixColumns([\Delta, 0, 0, 0])$

- Only 255 possible MixColumns outputs!

- Other 3 bytes can be faulted as well (but only one at a time)

- MixColumns([Δ, 0, 0, 0])

- MixColumns([0, Δ, 0, 0])

- MixColumns([0, 0, Δ, 0])

- MixColumns( $[0, 0, 0, \Delta]$ )

- Model byte fault using (unknown) difference  $\Delta \colon \mathit{v}_1' = \mathit{v}_1 \oplus \Delta$

- MixColumns: Linear operation, 4 byte input: MixColumns([ $v_1 \oplus \Delta, v_2, v_3, v_4$ ]) = MixColumns([ $v_1 \quad , v_2, v_3, v_4$ ])  $\oplus$  MixColumns([ $\Delta, 0, 0, 0$ ])

- Observe: 4 byte input, but only 1 is active in  $MixColumns([\Delta, 0, 0, 0])$

- Only 255 possible MixColumns outputs!

- Other 3 bytes can be faulted as well (but only one at a time)

- MixColumns([Δ, 0, 0, 0])

- MixColumns([0, Δ, 0, 0])

- MixColumns([0, 0, Δ, 0])

- MixColumns([0, 0, 0,  $\Delta$ ])

- $\bullet \ \ 4 \times 255 = 1020 \ possible \ MixColumns \ outputs \\$

- Precompute all of them

- Fault random byte before MixColumns9

- Determine affected column by checking output difference (only 4 ciphertext bytes will differ, check which ones)

- Fault random byte before MixColumns9

- Determine affected column by checking output difference (only 4 ciphertext bytes will differ, check which ones)

- Enumerate 2<sup>32</sup> combinations of affected RK<sub>10</sub>

- Compute back to output of MixColumns9 (for both, valid c and faulty c')

- Test if difference is in precomputed list

- $\rightarrow$  If yes then keep key candidate

- Fault random byte before MixColumns9

- Determine affected column by checking output difference (only 4 ciphertext bytes will differ, check which ones)

- Enumerate 2<sup>32</sup> combinations of affected RK<sub>10</sub>

- Compute back to output of MixColumns9 (for both, valid c and faulty c')

- Test if difference is in precomputed list

- $\rightarrow$  If yes then keep key candidate

- Problem: We don't want to try 2<sup>32</sup> keys ...

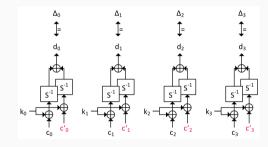

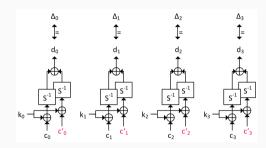

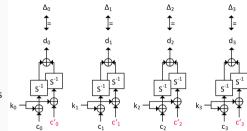

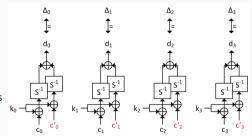

# **Efficient Implementation of the Attack**

- 1. Compute all 1020 possible MC output differences

- MC(1...255, 0, 0, 0), MC(0, 1...255, 0, 0), ...

#### **Efficient Implementation of the Attack**

- 1. Compute all 1020 possible MC output differences

- MC(1...255, 0, 0, 0), MC(0, 1...255, 0, 0), ...

- 2. Predict differences for each key byte individually

- 4 positions  $\times$  256 values = 1024 combinations

- Precompute them once

## **Efficient Implementation of the Attack**

- 1. Compute all 1020 possible MC output differences

- MC(1...255, 0, 0, 0), MC(0, 1...255, 0, 0), ...

- 2. Predict differences for each key byte individually

- 4 positions  $\times$  256 values = 1024 combinations

- Precompute them once

- 3. Loop over possible differences:

- For each difference  $(\Delta_0, \Delta_1, \Delta_2, \Delta_3)$ :

- Add all combinations of key bytes where  $(\Delta_0 = d_0, \Delta_1 = d_1, \ldots)$  to a list of potential keys

- 1. Compute all 1020 possible MC output differences

- MC(1...255, 0, 0, 0), MC(0, 1...255, 0, 0), ...

- 2. Predict differences for each key byte individually

- 4 positions  $\times$  256 values = 1024 combinations

- Precompute them once

- 3. Loop over possible differences:

- For each difference  $(\Delta_0, \Delta_1, \Delta_2, \Delta_3)$ :

- Add all combinations of key bytes where  $(\Delta_0 = d_0, \Delta_1 = d_1, \ldots)$  to a list of potential keys

- 4. Use second faulty/correct pair

- Loop over remaining key candidates from previous step

- For each: Test if predicted difference is in precomputed list

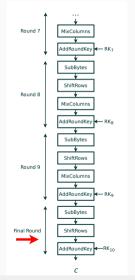

• Faulting between AddRoundKey8 - SubBytes9?

- Faulting between AddRoundKey8 SubBytes9?

- Fault model: Random fault in 1 byte

- Attack possible!

- Leads to exactly the same scenario as previously (1 byte in MixColumns9 is incorrect)

- Faulting between AddRoundKey8 SubBytes9?

- Fault model: Random fault in 1 byte

- Attack possible!

- Leads to exactly the same scenario as previously (1 byte in MixColumns9 is incorrect)

- → Powerful attack that requires at least 8 faults (at 4 locations) for full key recovery

- Faulting between AddRoundKey8 SubBytes9?

- Fault model: Random fault in 1 byte

- Attack possible!

- Leads to exactly the same scenario as previously (1 byte in MixColumns9 is incorrect)

- → Powerful attack that requires at least 8 faults (at 4 locations) for full key recovery

- But can we do even better?

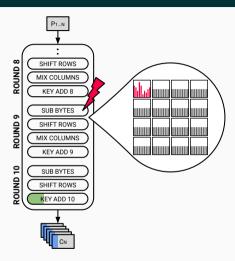

• Faulting between AddRoundKey7 - MixColumns8

- Faulting between AddRoundKey7 MixColumns8

- Fault model: Random fault in 1 byte

- Attack possible!

- Observation: faulting 1 byte

- ightarrow All 4 bytes in column affected later

- ShiftRows9 distributes the 4 bytes to 4 different columns

• Single-byte difference in each column with just 1 fault!

- Single-byte difference in each column with just 1 fault!

- Full key recovery with just 2 faults (by performing Priet's attack 4×)

- Single-byte difference in each column with just 1 fault!

- Full key recovery with just 2 faults (by performing Priet's attack  $4\times$ )

- Problem: harder to detect if fault injection is exploitable

- Before: 4 bytes different → likely exploitable

- Now: All bytes different, did we really hit single byte before MC8 or something else?

• Task 4: Piret's Attack

- Task 4: Piret's Attack

- Task 4.1: Develop the attack using simulated faults

- Use "Excel implementation" of AES for that

- Also very useful for debugging

- Task 4: Piret's Attack

- Task 4.1: Develop the attack using simulated faults

- Use "Excel implementation" of AES for that

- Also very useful for debugging

- Task 4.2: Repeat attack with the CW board (voltage glitches)

- Task 4: Piret's Attack

- Task 4.1: Develop the attack using simulated faults

- Use "Excel implementation" of AES for that

- Also very useful for debugging

- Task 4.2: Repeat attack with the CW board (voltage glitches)

- Task 4.3: Implement and test a countermeasure against DFA

- Task 4: Piret's Attack

- Task 4.1: Develop the attack using simulated faults

- Use "Excel implementation" of AES for that

- Also very useful for debugging

- Task 4.2: Repeat attack with the CW board (voltage glitches)

- Task 4.3: Implement and test a countermeasure against DFA

- In all cases: Recovering 4 bytes of the last roundkey is sufficient

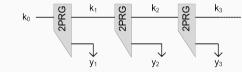

# Statistical Fault Attacks

• Exploit faulty ciphertexts only

- Exploit faulty ciphertexts only

- Plaintexts can be unknown but need to vary

- "Opposite" requirement compared to differential attacks

- Exploit faulty ciphertexts only

- Plaintexts can be unknown but need to vary

- "Opposite" requirement compared to differential attacks

- Usually need more than 2 faulted encryptions

- Exploit faulty ciphertexts only

- Plaintexts can be unknown but need to vary

- "Opposite" requirement compared to differential attacks

- Usually need more than 2 faulted encryptions

- Key recovery exploits statistical distributions of state bytes (in contrast to differences)

## Countermeasures

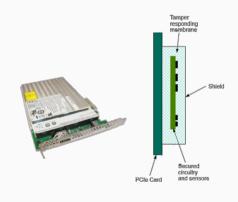

• Sensors to detect tampering

- Sensors to detect tampering

- Protocol/Mode level

- Limited key usage, no message twice ...

- Sensors to detect tampering

- Protocol/Mode level

- Limited key usage, no message twice ...

- Algorithmic countermeasures

- (Often) no hardware support needed

- Added redundancy to detect/correct errors

- Hiding (shuffling, random delays,...) to hinder precise fault injection, (masking)

- Sensors to detect anomalies

- Active meshes: Fine wire mesh across IC, disruption is detected

- Power surge sensors

- Temperature sensors

- Light sensors

- Sensors to detect anomalies

- Active meshes: Fine wire mesh across IC, disruption is detected

- Power surge sensors

- Temperature sensors

- Light sensors

- Example: IBM4767 Hardware Security Module

- Battery-backed monitoring, meshes, light sensors, temperature sensors, etc.

- Immediate deletion of keying material on tamper detection

- Precondition for differential fault attacks

- Encrypt same message twice with same key, get faulty output

- Break condition!

- Precondition for differential fault attacks

- Encrypt same message twice with same key, get faulty output

- Break condition!

- Frequent key update

- Use key for only 1 encryption, then update

- Precondition for differential fault attacks

- Encrypt same message twice with same key, get faulty output

- Break condition!

- Frequent key update

- Use key for only 1 encryption, then update

- Protocol that doesn't allow encryption of same message

- "Proper" modes needs randomization (nonce) anyway

- Problem: Decryption!

- Precondition for differential fault attacks

- Encrypt same message twice with same key, get faulty output

- Break condition!

- Frequent key update

- Use key for only 1 encryption, then update

- Protocol that doesn't allow encryption of same message

- "Proper" modes needs randomization (nonce) anyway

- Problem: Decryption!

- Authenticated encryption

- Tag verifies integrity of ciphertext

- Fault in decryption likely invalidates tag

- $\rightarrow$  No faulty output is released

- Old problem in communication: Noisy Channels

- Receiver wants to detect transmission errors and correct them

- Now: "Noise" source is attacker instead of channel

- Old problem in communication: Noisy Channels

- Receiver wants to detect transmission errors and correct them

- Now: "Noise" source is attacker instead of channel

- Solution: Redundancy

- Transmit redundant representation of data (more bits than actually needed)

- Use redundant information for error detection/correction

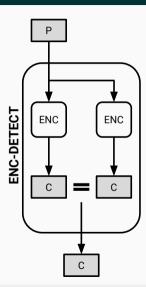

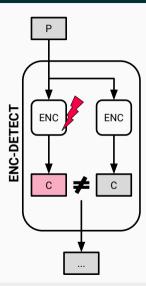

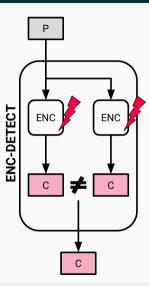

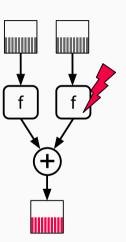

• Use redundancy to detect faults

- Use redundancy to detect faults

- ullet Fault detected o No ciphertext

- Use redundancy to detect faults

- ullet Fault detected o No ciphertext

- 2 identical faults necessary for attack

- Use redundancy to detect faults

- ullet Fault detected o No ciphertext

- 2 identical faults necessary for attack

- $\rightarrow\,$  More redundancy, Enc-Dec, etc...

**Breaking Countermeasures Again**

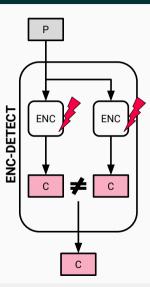

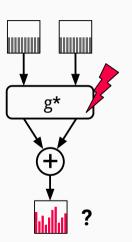

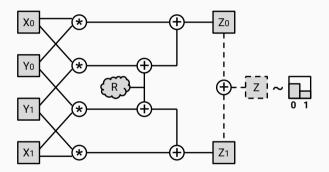

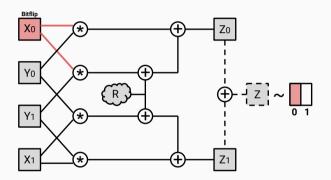

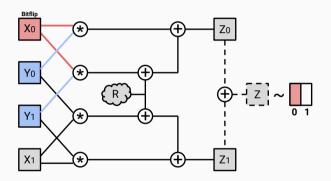

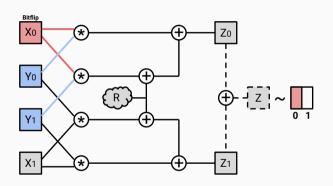

What about masked redundant implementations?

• Faulting single shares in linear functions does not work...

• Faulting single shares in linear functions does not work...

- Faulting single shares in linear functions does not work...

- Faulting all shares would work but is difficult...

- Faulting single shares in linear functions does not work...

- Faulting all shares would work but is difficult...

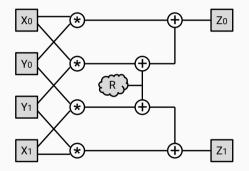

- Can faulting single shares in non-linear functions lead to a bias in the unshared value?

#### Also works with:

- Other types of faults

- Higher-order masking

- Threshold Implementations

• Fault attacks can be quite tricky to deal with...

- Fault attacks can be quite tricky to deal with...

- Can still be mitigated with:

- Carefully crafted cipher implementations + redundancy (assuming an attacker injects only up to x faults)

- Cryptographic modes/protocols that limit key usage

- Fault attacks can be quite tricky to deal with...

- Can still be mitigated with:

- Carefully crafted cipher implementations + redundancy (assuming an attacker injects only up to x faults)

- Cryptographic modes/protocols that limit key usage

- In practice one also often also relies on:

- Hiding to decrease attack performance

- Sensor-based countermeasures if available

- This is the last actual lecture of SCS

- Monday 24<sup>th</sup>: EX2 Deadline

## Thank you!

**Questions:**

rishub.nagpal@iaik.tugraz.at Discord

# Fault Attacks

Side-Channel Security

### Rishub Nagpal

June 13, 2024

IAIK - Graz University of Technology