# Digital System Integration and Programming

Barbara Gigerl, Rishub Nagpal October 5th, 2022

#### Outline

1. Digital system integration and programming

#### Outline

- 1. Digital system integration and programming

- 2. About this course

#### Outline

- 1. Digital system integration and programming

- 2. About this course

- 3. Outlook: Projects

# What is digital system integration and programming?

#### Digital system integration

- Digital systems: very complex

- System integration: connect multiple complex systems to achieve a certain goal

# What is digital system integration and programming?

#### Digital system integration

- Digital systems: very complex

- System integration: connect multiple complex systems to achieve a certain goal

#### ...and programming

Hardware and Software

# What is digital system integration and programming?

#### Digital system integration

- Digital systems: very complex

- System integration: connect multiple complex systems to achieve a certain goal

#### ...and programming

Hardware and Software

A **System-on-a-Chip (SoC)** is a complex system which:

consists of several components.

- consists of several components.

- Each component itself is a complex system.

- consists of several components.

- Each component itself is a complex system.

- CPU

- consists of several components.

- Each component itself is a complex system.

- CPU

- Memory

- consists of several components.

- Each component itself is a complex system.

- CPU

- Memory

- Bus architectures

- consists of several components.

- Each component itself is a complex system.

- CPU

- Memory

- Bus architectures

- I/O modules

- consists of several components.

- Each component itself is a complex system.

- CPU

- Memory

- Bus architectures

- I/O modules

- Co-processors

- consists of several components.

- Each component itself is a complex system.

- CPU

- Memory

- Bus architectures

- I/O modules

- Co-processors

- Analog circuits

- consists of several components.

- Each component itself is a complex system.

- CPU

- Memory

- Bus architectures

- I/O modules

- Co-processors

- Analog circuits

- **...**

#### A quick history

1970s: VLSI design

- 1970s: VLSI design

- VLSI = Very large-scale integration

- 1970s: VLSI design

- VLSI = Very large-scale integration

- Combining millions of MOS transistors into an integrated circuit

- 1970s: VLSI design

- VLSI = Very large-scale integration

- Combining millions of MOS transistors into an integrated circuit

- 1990s: System-on-a-chip

- 1970s: VLSI design

- VLSI = Very large-scale integration

- Combining millions of MOS transistors into an integrated circuit

- 1990s: System-on-a-chip

- System integration: integration of a complete system, that until recently consisted of multiple ICs, onto a single IC (a SoC)

- 1970s: VLSI design

- VLSI = Very large-scale integration

- Combining millions of MOS transistors into an integrated circuit

- 1990s: System-on-a-chip

- System integration: integration of a complete system, that until recently consisted of multiple ICs, onto a single IC (a SoC)

- Today: SoC is the state-of-the-art principle for designing chips.

Smartphones

Used in iPhone XS, XS Max, XR

- Used in iPhone XS, XS Max, XR

- 7nm CMOS, 6.9 billion transistors

- Used in iPhone XS, XS Max, XR

- 7nm CMOS, 6.9 billion transistors

- Components:

- Used in iPhone XS, XS Max, XR

- 7nm CMOS, 6.9 billion transistors

- Components:

- 64-bit ARMv8.3A (6 performance CPUs, 4 energy-efficient CPUs)

- Used in iPhone XS, XS Max, XR

- 7nm CMOS, 6.9 billion transistors

- Components:

- 64-bit ARMv8.3A (6 performance CPUs, 4 energy-efficient CPUs)

- Four-core GPU

- Used in iPhone XS, XS Max, XR

- 7nm CMOS, 6.9 billion transistors

- Components:

- 64-bit ARMv8.3A (6 performance CPUs, 4 energy-efficient CPUs)

- Four-core GPU

- Neural Engine with 8 cores

- Used in iPhone XS, XS Max, XR

- 7nm CMOS, 6.9 billion transistors

- Components:

- 64-bit ARMv8.3A (6 performance CPUs, 4 energy-efficient CPUs)

- Four-core GPU

- Neural Engine with 8 cores

- **-** ...

### Example: Qualcomm Snapdragon 865

Used in smartphones by ZTE, Sony, OnePlus, LG, ...

# Example: Qualcomm Snapdragon 865

- Used in smartphones by ZTE, Sony, OnePlus, LG, ...

- 7nm CMOS

### Example: Qualcomm Snapdragon 865

- Used in smartphones by ZTE, Sony, OnePlus, LG, ...

- 7nm CMOS

- Components:

- Used in smartphones by ZTE, Sony, OnePlus, LG, ...

- 7nm CMOS

- Components:

- Several ARM Cortex-A77 and Cortex-A55-based CPUs

- Used in smartphones by ZTE, Sony, OnePlus, LG, ...

- 7nm CMOS

- Components:

- Several ARM Cortex-A77 and Cortex-A55-based CPUs

- Deidcated processor for ISP for photos and videos

- Used in smartphones by ZTE, Sony, OnePlus, LG, ...

- 7nm CMOS

- Components:

- Several ARM Cortex-A77 and Cortex-A55-based CPUs

- Deidcated processor for ISP for photos and videos

- Wi-Fi

- Used in smartphones by ZTE, Sony, OnePlus, LG, ...

- 7nm CMOS

- Components:

- Several ARM Cortex-A77 and Cortex-A55-based CPUs

- Deidcated processor for ISP for photos and videos

- Wi-Fi

- SPU: dedicated subsystem for boot-loader, key management unit, crypto accelerators, ...

SoC for industrial applications

- SoC for industrial applications

- Used in thermostats, firewalls, Lego Mindstorms

- SoC for industrial applications

- Used in thermostats, firewalls, Lego Mindstorms

- 1 GHz ARM CPU

- SoC for industrial applications

- Used in thermostats, firewalls, Lego Mindstorms

- 1 GHz ARM CPU

- On-chip quad-core PRU (Programmable Realtime Unit)

#### A traditional SoC consists of:

Processor(s): mostly ARM cores

- Processor(s): mostly ARM cores

- GPU: depending on the field of application, ranging from simple cores for small LCDs to 4k screens

- Processor(s): mostly ARM cores

- GPU: depending on the field of application, ranging from simple cores for small LCDs to 4k screens

- Co-processors: for security, real-time signal processing, ...

- Processor(s): mostly ARM cores

- GPU: depending on the field of application, ranging from simple cores for small LCDs to 4k screens

- Co-processors: for security, real-time signal processing, ...

- I/O interfaces: Ethernet, SPI, USB, ADC, ...

- Processor(s): mostly ARM cores

- GPU: depending on the field of application, ranging from simple cores for small LCDs to 4k screens

- Co-processors: for security, real-time signal processing, ...

- I/O interfaces: Ethernet, SPI, USB, ADC, ...

- A bus connecting all components: AMBA, AXI, CoreConnect, ...

**Advantages**

### **Advantages**

Low silicon area

### **Advantages**

- Low silicon area

- Power efficiency (no need for complex component wiring)

### **Advantages**

- Low silicon area

- Power efficiency (no need for complex component wiring)

- Low manufacturing costs

### **Advantages**

- Low silicon area

- Power efficiency (no need for complex component wiring)

- Low manufacturing costs

- Smaller power supply unit

### **Advantages**

- Low silicon area

- Power efficiency (no need for complex component wiring)

- Low manufacturing costs

- Smaller power supply unit

### **Advantages**

- Low silicon area

- Power efficiency (no need for complex component wiring)

- Low manufacturing costs

- Smaller power supply unit

- Resulting system is very complex

- High design and development costs

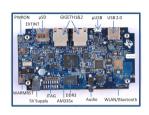

# SoC Design Methodology

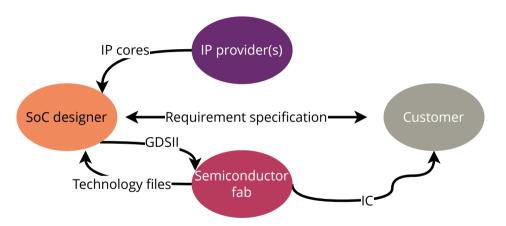

## SoC Players

- GDSII: data format to describe ICs

- Technology file: information about manufacturing (metals, IC layers, ...)

### Who are we?

### Barbara Gigerl

PhD student @ Graz University of Technology

Formal Verification of Side-Channel Protected Implementations

**☑** barbara.gigerl@iaik.tugraz.at

**▽** sip-team@iaik.tugraz.at

### Who are we?

### **Rishub Nagpal**

PhD student @ Graz University of Technology

Power side-channel attacks and defenses for cryptographic implementations

▼ rishub.nagpal@lamarr.at

**▽** sip-team@iaik.tugraz.at

## **Topics for Master Thesis**

```

Looking for a master thesis?

```

```

\rightarrow \texttt{https://www.iaik.tugraz.at/teaching/master-thesis/} We have lots of interesting open topics:)

```

### Alternatively, email us:

- barbara.gigerl@iaik.tugraz.at

- rishub.nagpal@lamarr.at

#### Contact

General information: https://www.iaik.tugraz.at/sip

- Questions and concerns by E-Mail mailto:sip-team@iaik.tugraz.at

- Questions and concerns via Discord https://discord.gg/9KKGfndsD5

We focus on the front-end design

- We focus on the front-end design

- We use an FPGA in order to build a prototype of our SoC

- We focus on the front-end design

- We use an FPGA in order to build a prototype of our SoC

- Our Platform: Zybo Zynq Boards

- We focus on the front-end design

- We use an FPGA in order to build a prototype of our SoC

- Our Platform: Zybo Zynq Boards

- Xilinx FPGA

- We focus on the front-end design

- We use an FPGA in order to build a prototype of our SoC

- Our Platform: Zybo Zynq Boards

- Xilinx FPGA

- 650Mhz dual-core Cortex-A9 processor

- We focus on the front-end design

- We use an FPGA in order to build a prototype of our SoC

- Our Platform: Zybo Zynq Boards

- Xilinx FPGA

- 650Mhz dual-core Cortex-A9 processor

- HDMI, VGA, USB, SPI, Ethernet, Audio, ...

- We focus on the front-end design

- We use an FPGA in order to build a prototype of our SoC

- Our Platform: Zybo Zynq Boards

- Xilinx FPGA

- 650Mhz dual-core Cortex-A9 processor

- HDMI, VGA, USB, SPI, Ethernet, Audio, ...

- Connected via AXI bus

### Goals

Build a working prototype

### Goals

- Build a working prototype

- Project management and self-organization

### Goals

- Build a working prototype

- Project management and self-organization

- Presentation of: ideas, results, technology in English

#### Goals

- Build a working prototype

- Project management and self-organization

- Presentation of: ideas, results, technology in English

- Preparation for project/thesis

#### SIP addresses advanced-level students. You need:

Knowledge about hardware including a HDL (Verilog/VHDL)

(Computer Organization and Networks is probably not enough)

- Knowledge about hardware including a HDL (Verilog/VHDL)

(Computer Organization and Networks is probably not enough)

- Very good C/C++ skills

- Knowledge about hardware including a HDL (Verilog/VHDL)

(Computer Organization and Networks is probably not enough)

- Very good C/C++ skills

- Knowledge about Linux

- Knowledge about hardware including a HDL (Verilog/VHDL)

(Computer Organization and Networks is probably not enough)

- Very good C/C++ skills

- Knowledge about Linux

- Buildroot/Yocto, kernel modules, drivers, device trees, GPIO

- Knowledge about hardware including a HDL (Verilog/VHDL)

(Computer Organization and Networks is probably not enough)

- Very good C/C++ skills

- Knowledge about Linux

- Buildroot/Yocto, kernel modules, drivers, device trees, GPIO

- Knowledge about FPGAs, bus protocols, CPUs, networks

- Knowledge about hardware including a HDL (Verilog/VHDL)

(Computer Organization and Networks is probably not enough)

- Very good C/C++ skills

- Knowledge about Linux

- Buildroot/Yocto, kernel modules, drivers, device trees, GPIO

- Knowledge about FPGAs, bus protocols, CPUs, networks

- Very good time-management skills

- Knowledge about hardware including a HDL (Verilog/VHDL)

(Computer Organization and Networks is probably not enough)

- Very good C/C++ skills

- Knowledge about Linux

- Buildroot/Yocto, kernel modules, drivers, device trees, GPIO

- Knowledge about FPGAs, bus protocols, CPUs, networks

- Very good time-management skills

- Good presentation skills

#### We offer:

Project driven work (group-oriented, project-centric)

- Project driven work (group-oriented, project-centric)

- Hands-on project with real hardware

- Project driven work (group-oriented, project-centric)

- Hands-on project with real hardware

- Upgrading of soft skills

- Project driven work (group-oriented, project-centric)

- Hands-on project with real hardware

- Upgrading of soft skills

- Presentations

- Project driven work (group-oriented, project-centric)

- Hands-on project with real hardware

- Upgrading of soft skills

- Presentations

- Speaking English

- Project driven work (group-oriented, project-centric)

- Hands-on project with real hardware

- Upgrading of soft skills

- Presentations

- Speaking English

- Group communication

#### We expect:

Investment of time

- Investment of time

- SIP: 3 VU (5 ECTS)

- Investment of time

- SIP: 3 VU (5 ECTS)

- $5 \times 25 = 125$  hours work = 28 days of 8 hours

- Investment of time

- SIP: 3 VU (5 ECTS)

- $5 \times 25 = 125$  hours work = 28 days of 8 hours

- Active communication within your group

- Investment of time

- SIP: 3 VU (5 ECTS)

- $5 \times 25 = 125$  hours work = 28 days of 8 hours

- Active communication within your group

- Active participation, presence during lectures

#### Your grade consists of:

• Project 1: 20%

- Project 1: 20%

- Individual work, independent submissions

- Project 1: 20%

- Individual work, independent submissions

- Project 2: 50%

- Project 1: 20%

- Individual work, independent submissions

- Project 2: 50%

- Team work in groups of 2 or 3 students

- Project 1: 20%

- Individual work, independent submissions

- Project 2: 50%

- Team work in groups of 2 or 3 students

- Seminar presentation: 30%

- Project 1: 20%

- Individual work, independent submissions

- Project 2: 50%

- Team work in groups of 2 or 3 students

- Seminar presentation: 30%

- Selection from course catalog OR suggest your own topic

- Project 1: 20%

- Individual work, independent submissions

- Project 2: 50%

- Team work in groups of 2 or 3 students

- Seminar presentation: 30%

- Selection from course catalog OR suggest your own topic

- Slides are reviewed by us (submit until Monday evening)

- Project 1: 20%

- Individual work, independent submissions

- Project 2: 50%

- Team work in groups of 2 or 3 students

- Seminar presentation: 30%

- Selection from course catalog OR suggest your own topic

- Slides are reviewed by us (submit until Monday evening)

- Bonus points for questions during/after seminar presentations

#### Team work

- Team Size for Project 1: 1

- Team Size for Project 2: 3

- Team Size for Seminar presentation: 1

1. Find a group

- 1. Find a group

- 2. Find and register your group: mailto:sip-team@iaik.tugraz.at

- 1. Find a group

- 2. Find and register your group: mailto:sip-team@iaik.tugraz.at

- 3. Wait for the confirmation mail to get your group number

- 1. Find a group

- 2. Find and register your group: mailto:sip-team@iaik.tugraz.at

- 3. Wait for the confirmation mail to get your group number

- 4. Decide when to pick up the hardware (IF01052, Mo-Fr 10:00-16:00<sup>1</sup>)

- 1. Find a group

- 2. Find and register your group: mailto:sip-team@iaik.tugraz.at

- 3. Wait for the confirmation mail to get your group number

- 4. Decide when to pick up the hardware (IF01052, Mo-Fr 10:00-16:00<sup>1</sup>)

- 5. Choose a seminar topic

- 1. Find a group

- 2. Find and register your group: mailto:sip-team@iaik.tugraz.at

- 3. Wait for the confirmation mail to get your group number

- 4. Decide when to pick up the hardware (IF01052, Mo-Fr 10:00-16:00<sup>1</sup>)

- 5. Choose a seminar topic

- 6. Register for a seminar topic: https://bit.ly/3dZjipp

<sup>&</sup>lt;sup>1</sup>You can try your luck before/after

- 1. Find a group

- 2. Find and register your group: mailto:sip-team@iaik.tugraz.at

- 3. Wait for the confirmation mail to get your group number

- 4. Decide when to pick up the hardware (IF01052, Mo-Fr 10:00-16:00<sup>1</sup>)

- 5. Choose a seminar topic

- 6. Register for a seminar topic: https://bit.ly/3dZjipp

- 7. Receive your git repositories (by email)

<sup>&</sup>lt;sup>1</sup>You can try your luck before/after

#### Schedule of SIP 2022

#### **Project meetings**

Regular weekly meetings: Wednesday 10:00 - 12:00, IFEG042

- Regular weekly meetings: Wednesday 10:00 12:00, IFEG042

- Program for each project meeting

- Regular weekly meetings: Wednesday 10:00 12:00, IFEG042

- Program for each project meeting

- 1. Questions, problems about the project

- Regular weekly meetings: Wednesday 10:00 12:00, IFEG042

- Program for each project meeting

- 1. Questions, problems about the project

- 2. Each team briefly (1-2 sentences) comments on own project progress

- Regular weekly meetings: Wednesday 10:00 12:00, IFEG042

- Program for each project meeting

- 1. Questions, problems about the project

- 2. Each team briefly (1-2 sentences) comments on own project progress

- 3. Seminar talk + discussion

- Regular weekly meetings: Wednesday 10:00 12:00, IFEG042

- Program for each project meeting

- 1. Questions, problems about the project

- 2. Each team briefly (1-2 sentences) comments on own project progress

- 3. Seminar talk + discussion

- 4. Seminar talk + discussion

- Regular weekly meetings: Wednesday 10:00 12:00, IFEG042

- Program for each project meeting

- 1. Questions, problems about the project

- 2. Each team briefly (1-2 sentences) comments on own project progress

- 3. Seminar talk + discussion

- 4. Seminar talk + discussion

- 5. ...

# Preliminary timeline

| Date   | Topic                                                                |

|--------|----------------------------------------------------------------------|

| 05.10. | Kick-off / Introduction to Seminar Topics / SoC Design Flow Tutorial |

| 12.10. | Embedded Linux Tutorial / Presentation Project 1                     |

| 19.10. | Debugging Tutorial                                                   |

| 26.10. | Bank holiday (no meeting)                                            |

| 2.11.  | Bank holiday (no meeting)                                            |

| 9.11.  | Presentation Project 2a+2b / Seminar talks                           |

| 16.11. | Seminar talks                                                        |

| 23.11. | Seminar talks                                                        |

| 30.11. | Seminar talks                                                        |

| 7.12.  | Seminar talks                                                        |

| 14.12. | Seminar talks                                                        |

| 11.01. | Seminar talks                                                        |

| 18.01. | Seminar talks                                                        |

| 25.01. | Seminar talks                                                        |

# Important Dates and Deadlines

| Topic                          |

|--------------------------------|

| Deadline Group Registration    |

| Deadline Project 1             |

| Exercise Interviews Project 1  |

| Deadline Project 2a            |

| Exercise Interviews Project 2a |

| Deadline Project 2b            |

| Exercise Interviews Project 2a |

|                                |

Get to know the board and run through all steps

- Get to know the board and run through all steps

- Design hardware, build a driver, write an application

- Get to know the board and run through all steps

- Design hardware, build a driver, write an application

- Access the LEDs from a bare-metal application and from within Linux

- Get to know the board and run through all steps

- Design hardware, build a driver, write an application

- Access the LEDs from a bare-metal application and from within Linux

- No team work; everybody should do all steps (share your board within group)

- Get to know the board and run through all steps

- Design hardware, build a driver, write an application

- Access the LEDs from a bare-metal application and from within Linux

- No team work; everybody should do all steps (share your board within group)

- Aim: After completing, everybody should have the same basic knowledge.

# Project 2: Display for Encrypted Images

- Use knowledge from Project 1 to build larger system

- Receive encrypted image via Ethernet, decrypt it in hardware and display it via HDMI

- Team work

- Aim: Get some deeper understanding of the topic