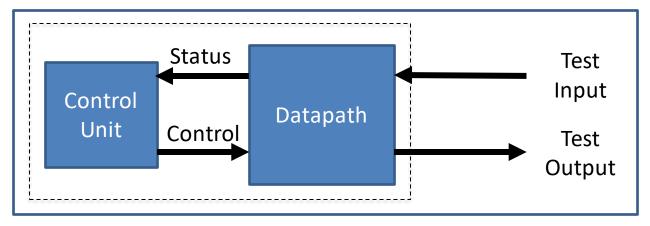

# Hardware Description Language (HDL): Overview of a Digital System

- Datapath

- Performs data processing

- Control Unit (Finite State Machine)

- Generates control signals to control the datapath

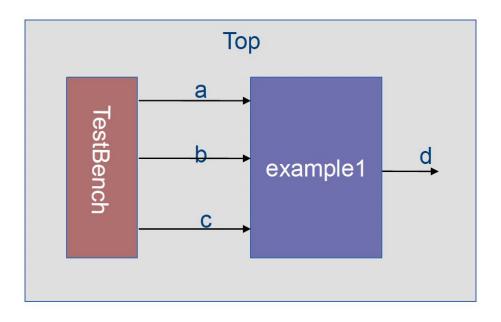

- Testbench

- Used to verify the functional correctness of the design (for simulation)

Testbench

## Hardware Description Language (HDL): Definition

- It is **NOT** a programming language.

- It is used to describe any digital circuit.

- i.e., you can describe circuit elements and connections between them.

- Many languages available for RTL Modeling: VHDL, Verilog, SystemVerilog

- Verilog is simple and similar to C

- Verilog has more than half of the world digital design market

- Many free resources are available:

- http://www.asic-world.com/verilog/veritut.html

- https://www.chipverify.com/verilog/

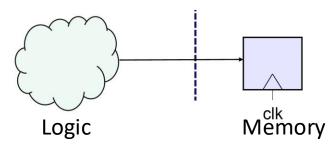

## Hardware Description Language (HDL): Logic and Memory

- Register Transfer Level: An abstract level used to describe the operation of synchronous digital circuits.

- Logic Functions (computation)

- Any combinatorial computation

- Memory (update)

- Flip-Flop: edge sensitive

- Latch: level sensitive (WE WILL NOT USE)

• Logical, arithmetic and conditional operators

| Syntax   | Operation         |  |

|----------|-------------------|--|

| ~        | Bit-wise negation |  |

| &        | AND               |  |

| ! &      | NAND              |  |

|          | OR                |  |

| ~        | NOR               |  |

| ^        | XOR               |  |

| ^~ or ~^ | XNOR              |  |

| Syntax | Operation      |

|--------|----------------|

| +      | Addition       |

| _      | Subtraction    |

| *      | Multiplication |

| /      | Division       |

| olo    | Modulo         |

| <<     | Left shift     |

| >>     | Right shift    |

| Syntax | Operation             |

|--------|-----------------------|

| ==     | Equality              |

| !=     | Inequality            |

| <      | Less than             |

| <=     | Less than or equal    |

| >      | Greater than          |

| >=     | Greater than or equal |

```

i.e.,

c = ~a;

c = a & b;

```

Operator precedence is important.

| <b>Verilog Operator</b> | Name                      | Functional Group |

|-------------------------|---------------------------|------------------|

| []                      | bit-select or part-select |                  |

| ()                      | parenthesis               |                  |

| 1                       | logical negation          | logical          |

| ~                       | negation                  | bit-wise         |

| &                       | reduction AND             | reduction        |

|                         | reduction OR              | reduction        |

| ~&                      | reduction NAND            | reduction        |

| ~                       | reduction NOR             | reduction        |

| . ^ .                   | reduction XOR             | reduction        |

| ~^ or ^~                | reduction XNOR            | reduction        |

| +                       | unary (sign) plus         | arithmetic       |

| -                       | unary (sign) minus        | arithmetic       |

| { }                     | concatenation             | concatenation    |

| {{ }}                   | replication               | replication      |

| *                       | multiply                  | arithmetic       |

| /                       | divide                    | arithmetic       |

| %                       | modulus                   | arithmetic       |

| +                       | binary plus               | arithmetic       |

| -                       | binary minus              | arithmetic       |

| <<                      | shift left                | shift            |

| >>                      | shift right               | shift            |

| >                       | greater than              | relational       |

| >=                      | greater than or equal to  | relational       |

| <                       | less than                 | relational       |

| <=                      | less than or equal to     | relational       |

| ==                      | logical equality          | equality         |

| !=                      | logical inequality        | equality         |

| ===                     | case equality             | equality         |

| !==                     | case inequality           | equality         |

| &                       | bit-wise AND              | bit-wise         |

| ٨                       | bit-wise XOR              | bit-wise         |

| ^~ or ~^                | bit-wise XNOR             | bit-wise         |

|                         | bit-wise OR               | bit-wise         |

| &&                      | logical AND               | logical          |

|                         | logical OR                | logical          |

| ?:                      | conditional               | conditional      |

<sup>\*</sup> Table from: https://class.ece.uw.edu/cadta/verilog/operators.html

Operator precedence is important.

| Verilog Operator    | Name                                                                           | Functional Group                                     |

|---------------------|--------------------------------------------------------------------------------|------------------------------------------------------|

| []                  | bit-select or part-select                                                      |                                                      |

| ()                  | parenthesis                                                                    |                                                      |

| !                   | logical negation<br>negation                                                   | logical<br>bit-wise                                  |

| &<br> <br>~&        | reduction AND<br>reduction OR<br>reduction NAND                                | reduction<br>reduction<br>reduction                  |

| ~ <br>^<br>~^ or ^~ | reduction NOR<br>reduction XOR<br>reduction XNOR                               | reduction<br>reduction<br>reduction                  |

| + -                 | unary (sign) plus<br>unary (sign) minus                                        | arithmetic<br>arithmetic                             |

| { }                 | concatenation                                                                  | concatenation                                        |

| {{ }}               | replication                                                                    | replication                                          |

| *<br>/<br>%         | multiply<br>divide<br>modulus                                                  | arithmetic<br>arithmetic<br>arithmetic               |

| +                   | binary plus<br>binary minus                                                    | arithmetic<br>arithmetic                             |

| <<<br>>>            | shift left<br>shift right                                                      | shift<br>shift                                       |

| ><br>>=<br><<br><=  | greater than<br>greater than or equal to<br>less than<br>less than or equal to | relational<br>relational<br>relational<br>relational |

| ==<br>!=            | logical equality<br>logical inequality                                         | equality<br>equality                                 |

| ===<br>!==          | case equality<br>case inequality                                               | equality<br>equality                                 |

| &                   | bit-wise AND                                                                   | bit-wise                                             |

| ^~ or ~∧            | bit-wise XOR<br>bit-wise XNOR                                                  | bit-wise<br>bit-wise                                 |

|                     | bit-wise OR                                                                    | bit-wise                                             |

| &&                  | logical AND                                                                    | logical                                              |

|                     | logical OR                                                                     | logical                                              |

| ?:                  | conditional                                                                    | conditional                                          |

$$c0 = a + b << 2;$$

$a = 4, b = 1$

$c0 = (5 << 2) = 20$

<sup>\*</sup> Table from: https://class.ece.uw.edu/cadta/verilog/operators.html

Operator precedence is important.

| <b>Verilog Operator</b> | Name                            | Functional Group       |

|-------------------------|---------------------------------|------------------------|

| []                      | bit-select or part-select       |                        |

| ()                      | parenthesis                     |                        |

| !                       | logical negation                | logical                |

| ~                       | negation                        | bit-wise               |

| &                       | reduction AND                   | reduction              |

|                         | reduction OR                    | reduction              |

| ~&                      | reduction NAND                  | reduction              |

| ~                       | reduction NOR                   | reduction              |

| A A                     | reduction XOR<br>reduction XNOR | reduction<br>reduction |

| ~^ or ^~                |                                 |                        |

| +                       | unary (sign) plus               | arithmetic             |

| -                       | unary (sign) minus              | arithmetic             |

| { }                     | concatenation                   | concatenation          |

| {{ }}                   | replication                     | replication            |

| *                       | multiply                        | arithmetic             |

| /                       | divide                          | arithmetic             |

| %                       | modulus                         | arithmetic             |

| +                       | binary plus                     | arithmetic             |

| -                       | binary minus                    | arithmetic             |

| <<                      | shift left                      | shift                  |

| >>                      | shift right                     | shift                  |

| >                       | greater than                    | relational             |

| >=                      | greater than or equal to        |                        |

| <                       | less than                       | relational             |

| <=                      | less than or equal to           | relational             |

| ==                      | logical equality                | equality               |

| !=                      | logical inequality              | equality               |

| ===                     | case equality                   | equality               |

| !==                     | case inequality                 | equality               |

| &                       | bit-wise AND                    | bit-wise               |

| ٨                       | bit-wise XOR                    | bit-wise               |

| ^~ or ~^                | bit-wise XNOR                   | bit-wise               |

|                         | bit-wise OR                     | bit-wise               |

| &&                      | logical AND                     | logical                |

|                         | logical OR                      | logical                |

| ?:                      | conditional                     | conditional            |

$$c0 = a + b << 2;$$

$a = 4, b = 1$

$c0 = (5 << 2) = 20$

$c1 = a + (b << 2);$

$a = 4, b = 1$

$c1 = 4 + (1 << 2) = 8$

<sup>\*</sup> Table from: https://class.ece.uw.edu/cadta/verilog/operators.html

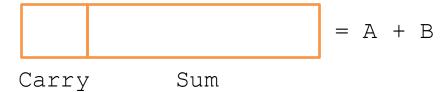

# **Verilog Operators - Example**

- Using + operator to design an adder

- 4-bit inputs and 5-bit output

- { } operator is used to concatenate signals

- Carry is 1-bit

- Sum is 4-bit

```

{Carry, Sum} = A + B;

```

- { { } } operator is used to repeat a signal

- Repeating Carry[0] bit four times

```

{Carry[0], Carry[0], Carry[0], Carry[0]} --> {4{Carry[0]}}

```

#### **Language Element - Literals**

- Literals are constant numbers (in binary, octal, decimal and hexadecimal).

- Literals as represented as:

```

<size>'<signed><radix>value

```

#### **Language Element - Literals**

- Literals are constant numbers (in binary, octal, decimal and hexadecimal).

- Literals as represented as:

```

<size>' <signed><radix>value

```

- e.g., A = 16' d12987;

- 16 indicates the bit size of the signal

- d indicates decimal representation is used.

- b or B -> binary

- o or 0 -> octal

- d or D -> decimal

- h or H -> hexadecimal

- No s after 'shows it is unsigned

- e.g., B = 20;

- If bit size, sign and radix are not specified, default representation is 32-bit unsigned decimal

#### **Language Element - Literals**

- Literals are constant numbers (in binary, octal, decimal and hexadecimal).

- Literals as represented as:

```

<size>' <signed><radix>value

```

- e.g., A = 16' d12987;

- 16 indicates the bit size of the signal

- d indicates decimal representation is used.

- b or B -> binary

- o or 0 -> octal

- d or D -> decimal

- h or H -> hexadecimal

- No s after 'shows it is unsigned

- e.g., B = 20;

- If bit size, sign and radix are not specified, default representation is 32-bit unsigned decimal.

# **Language Elements – Data Types**

- Bus definition

- n-bit data type declaration

- reg [n-1:0] a;wire [n-1:0] a;

- Part selection:

```

reg [31:0] a,b;

wire [16:0] sum;

assign sum = a[15:0]+ b[15:0];

```

# **Language Elements – Data Types**

- Bus definition

- n-bit data type declaration

- reg [n-1:0] a;

- wire [n-1:0] a;

- Part selection:

```

reg [31:0] a,b;

wire [16:0] sum;

assign sum = a[15:0]+ b[15:0];

```

- Verilog is case-sensitive

- reg [3:0] Rega, RegA;

- Net/Variable names cannot start with a number

- reg [3:0] 2num; X

- reg [3:0] num2;

## **Language Elements – Module and ports**

Verilog module declaration starts with module and ends with endmodule.

```

module module_name (<port list>);

// Module content

endmodule

```

- Module ports (by default, ports are considered as type wire):

- input

- output

- inout

## **Language Elements – Module and ports**

• Example:

```

module add_unit (a,b,c);

input [3:0] a,b;

output[4:0] c;

assign c = a+b;

endmodule

```

#### **Language Elements – Statements**

- Statements are used to drive nets

- There are two different methods to define Statements:

```

combinational (Blocking: =)

always

Combinational (Blocking: =)

Sequential (Non-blocking: <=)</pre>

```

- It is used to drive output and wire types. It is used to define combinational circuit parts.

- Order of assign statements is not important.

- When a variable at the RHS of assign statement changes, LHS is re-evaluated.

- It is used to drive output and wire types. It is used to define combinational circuit parts.

- Order of assign statements is not important.

- When a variable at the RHS of assign statement changes, LHS is re-evaluated.

```

module Module 1 (A, B, C, D, E);

input [3:0] A, B, C;

output[11:0] D, E;

wire [4:0] t1, t2, t3;

assign t1 = A + B;

assign t2 = A - B;

assign t3 = (C \ll 1);

assign D = (t1 * t2) + t3;

assign E = A * C;

endmodule

```

- It is used to drive output and wire types. It is used to define combinational circuit parts.

- Order of assign statements is not important.

- When a variable at the RHS of assign statement changes, LHS is re-evaluated.

```

module Module 1 (A, B, C, D, E);

input [3:0] A, B, C;

output[11:0] D, E;

wire [4:0] t1, t2, t3;

assign t1 = A + B;

assign t2 = A - B;

assign t3 = (C \ll 1);

assign D = (t1 * t2) + t3;

assign E = A * C;

endmodule

```

When A changes, the new values of t1, t2 and E are computed concurrently

- It is used to drive output and wire types. It is used to define combinational circuit parts.

- Order of assign statements is not important.

- When a variable at the RHS of assign statement changes, LHS is re-evaluated.

```

module Module 1 (A, B, C, D, E);

input [3:0] A, B, C;

output[11:0] D, E;

wire [4:0] t1, t2, t3;

assign t1 = A + B;

assign t2 = A - B;

assign t3 = (C \ll 1);

assign D = (t1 * t2) + t3;

assign E = A * C;

endmodule

```

- When A changes, the new values of t1, t2 and E are computed concurrently

- Since t1 and t2 are updated, D is re-evaluated

- It is used to drive output and wire types. It is used to define combinational circuit parts.

- Order of assign statements is not important.

- When a variable at the RHS of assign statement changes, LHS is re-evaluated.

```

module Module 1 (A, B, C, D, E);

input [3:0] A, B, C;

output[11:0] D, E;

wire [4:0] t1, t2, t3;

assign t1 = A + B;

assign t2 = A - B;

assign t3 = (C \ll 1);

assign D = (t1 * t2) + t3;

assign E = A * C;

endmodule

```

- When A changes, the new values of t1, t2 and E are computed concurrently

- Since t1 and t2 are updated, D is re-evaluated

- D does not update any net

No combinatorial loops

```

wire [7:0] b;

assign b = b + 1;

```

No combinatorial loops between signals in a clock cycle

# Language Elements – always Statement

- It is used to drive reg types. It is used to define both combinational and sequential parts.

- A sensitivity list is defined for each always block.

- It has signals that trigger the execution of the logic defined in always block

- Syntax:

```

always @(sensitivity list)

begin

<your logic>

end

```

#### Clock-sensitive synchronous design

```

always @(posedge clk)

begin

<your logic>

end

```

#### Combinational design

```

always @(*)

begin

<your logic>

end

```

# **Language Elements - Conditional Assignments**

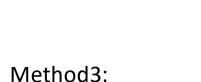

- Three ways to do conditional assignment.

- Method1: if/else if/else

```

always @ (*)

begin

if (S==1'b0)

Y = I0;

else

Y = I1;

end

```

Method2: case/endcase

```

always @ (*)

begin

case(S)

1'b0: Y = I0;

1'b1: Y = I1;

endcase

end

```

```

always @ (*)

begin

Y = (S) ? I1 : I0;

end

```

MUX

## **Language Elements - Conditional Assignments**

- Three ways to do conditional assignment.

- Method1: if/else if/else

```

always @ (*)

begin

if(S==1'b0)

Y = I0;

else

Y = I1;

end

```

For combinational circuits, never use incomplete conditional assignments!

Method2: case/endcase

```

always @ (*)

begin

case(S)

1'b0: Y = I0;

1'b1: Y = I1;

endcase

end

```

Method3:

```

always @ (*)

begin

Y =(S) ? I1 : I0;

end

```

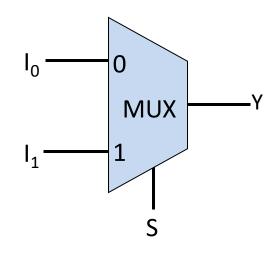

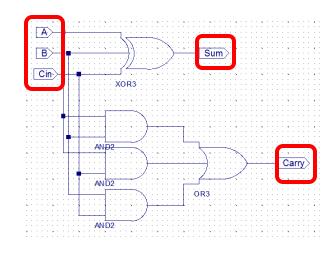

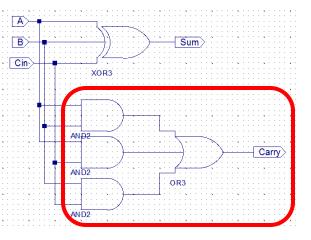

- module/endmodule is used to define the design

- A unique name must be given to each design in a project

```

module Full Adder

endmodule

```

- All I/Os must be defined in argument list. Order of the list is not important

- The polarity of the ports (input or output) must be defined at the beginning.

```

module Full Adder (A, B, Cin, Sum, Carry);

input A, B, Cin;

output Sum, Carry;

endmodule

```

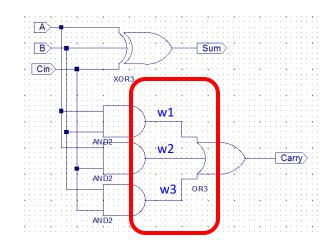

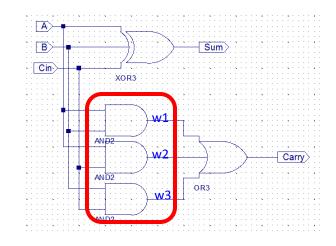

- There may be some interconnections between gates

- Gates are connected with nets which are defined as wire

```

module Full Adder (A, B, Cin, Sum, Carry);

input A, B, Cin;

output Sum, Carry;

wire w1, w2, w3;

endmodule

```

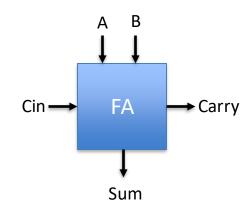

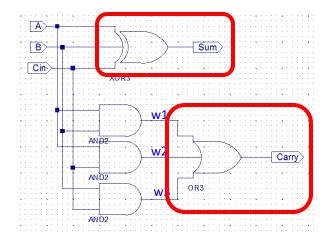

After the module is created and all I/Os and nets are defined, the interconnections may be defined.

```

module Full Adder (A, B, Cin, Sum, Carry);

input A, B, Cin;

output Sum, Carry;

wire w1, w2, w3;

assign w1 = A \& B;

assign w2 = A & Cin;

assign w3 = B & Cin;

endmodule

```

• After the module is created and all I/Os and nets are defined, the interconnections may be defined.

```

module Full Adder (A, B, Cin, Sum, Carry);

input A, B, Cin;

output Sum, Carry;

wire w1, w2, w3;

assign w1 = A \& B;

assign w2 = A \& Cin;

assign w3 = B \& Cin;

assign Carry = w1 | w2| w3;

assign Sum = A ^ B ^ Cin;

endmodule

```

- All interconnections do not have to be defined seperately.

- // (line comment) or /\* \*/ (block comment) may be used to add comments.

```

module Full_Adder (A, B, Cin, Sum, Carry);

input A, B, Cin; //inputs

output Sum, Carry; /*outputs*/

assign Carry = (A & B) | (A & Cin) | (B & Cin);

assign Sum = A ^ B ^ Cin;

endmodule

```

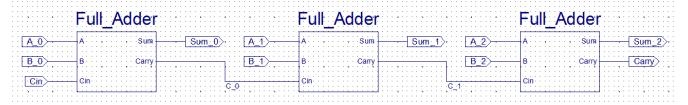

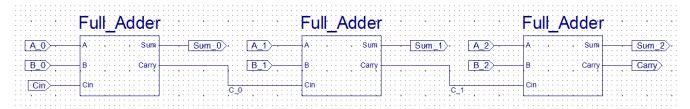

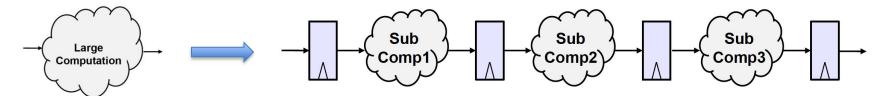

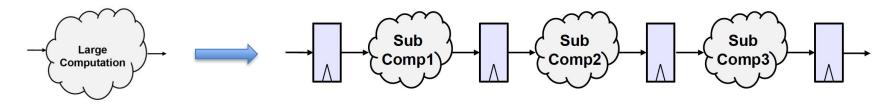

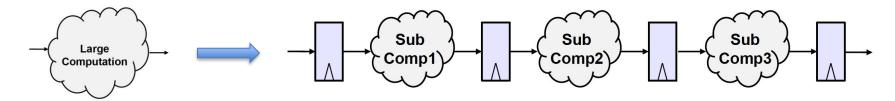

- Hierarchical Design

- A module may be used as a sub-module of another module.

- Hierarchical Design

- A module may be used as a sub-module of another module.

```

module RCA3 (A, B, Cin, S, Carry);

input [2:0] A, B;

input Cin;

output [2:0] S;

output Carry;

wire C_0, C_1;

Full_Adder FA0 (A[0], B[0], Cin, S[0], C_0);

Full_Adder FA1 (.A(A[1]), .B(B[1]), .Cin(C_0), .S(S[1]), .Carry(C_1));

Full_Adder FA2 (.S(S[2]), .B(B[2]), .Cin(C_1), .Carry(Carry), .A(A[2]));

endmodule

```

- Module Instantiation

- Firstly, the name of module, which is instantiated, is specified.

- Then, a unique name is given to each module.

```

Full_Adder FA0 (<ports>);

```

- Module Instantiation

- Firstly, the name of module, which is instantiated, is specified.

- Then, a unique name is given to each module.

```

Full_Adder FA0 (<ports>);

```

Finally, I/O connections of the module are defined. There are two methods:

#### A Sample Design: 3-bit Ripple Carry Adder

- Module Instantiation

- Firstly, the name of module, which is instantiated, is specified.

- Then, a unique name is given to each module.

```

Full_Adder FA0 (<ports>);

```

- Finally, I/O connections of the module are defined. There are two methods:

- Method1: Signal names are written inside the parenthesis. Signals have to be written in the same order of submodule argument list.

```

Full_Adder FA0 (A[0], B[0], Cin, S[0], C_0);

```

#### A Sample Design: 3-bit Ripple Carry Adder

- Module Instantiation

- Firstly, the name of module, which is instantiated, is specified.

- Then, a unique name is given to each module.

```

Full_Adder FA0 (<ports>);

```

- Finally, I/O connections of the module are defined. There are two methods:

- Method1: Signal names are written inside the parenthesis. Signals have to be written in the same order of submodule port list.

```

Full_Adder FA0 (A[0], B[0], Cin, S[0], C_0);

```

• Method2: Signals and ports are connected explicitly. Order of the signals is not important in this method.

```

Full_Adder FA0 (.A(A[0]), .B(B[0]), .Cin(Cin), .S(S[0]),

.Carry(C_0));

```

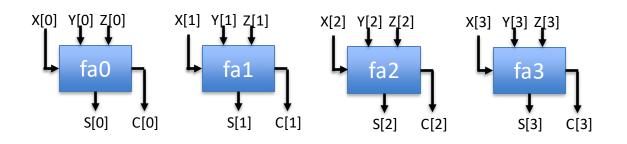

- A generate block is used to instantiate a module multiple times

- It must be coded in a module

```

genvar i;

generate

for(i=0; i<N; i=i+1)

begin

<module instantiation>

end

endgenerate

```

• (

```

for(int i=0; i<4; i++) {

s = Full_Adder(...);

}</pre>

```

Verilog

```

genvar i;

generate

for(i=0; i<4; i=i+1) begin

Full_Adder fa(...);

end

endgenerate</pre>

```

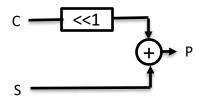

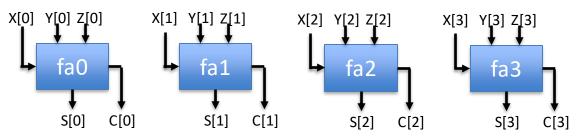

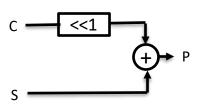

Example: 4-bit Carry Save Adder

Example: 4-bit Carry Save Adder

```

module CSA4 (X, Y, Z, P);

input [3:0] X, Y, Z;

output[5:0] P;

wire [3:0] C, S;

genvar i;

generate

for (i=0; i<4; i=i+1) begin</pre>

Full Adder fa(X[i], Y[i], Z[i], S[i], C[i]);

end

endgenerate

assign P = S + (C \ll 1);

endmodule

```

• Parameters are constants that allow a module to be re-used with different specifications

```

parameter PARAMETER_NAME = <value>;

```

• Parameters are constants that allow a module to be re-used with different specifications

```

parameter PARAMETER_NAME = <value>;

```

Example:

```

parameter N = 8;

wire [N-1:0] a,b;

wire [N:0] c;

assign c = a+b;

```

Example: Parameterized module

```

module CSA # (parameter N=4) (X, Y, Z, P);

input [N-1:0] X, Y, Z;

output[N+1:0] P;

wire [N-1:0] C, S;

genvar i;

generate

for (i=0; i<N; i=i+1) begin</pre>

Full Adder fa(X[i], Y[i], Z[i], S[i], C[i]);

end

endgenerate

assign P = S + (C << 1);

endmodule

```

Example: Parameterized module

```

module CSA # (parameter N=4) (X, Y, Z, P);

input [N-1:0] X, Y, Z;

output[N+1:0] P;

wire [N-1:0] C, S;

genvar i;

generate

for (i=0; i<N; i=i+1) begin</pre>

Full Adder fa(X[i], Y[i], Z[i], S[i], C[i]);

end

endgenerate

assign P = S + (C \ll 1);

endmodule

```

How to instantiate a parameterized module?

```

CSA \#(.N(8)) unit(X,Y,Z,P);

```

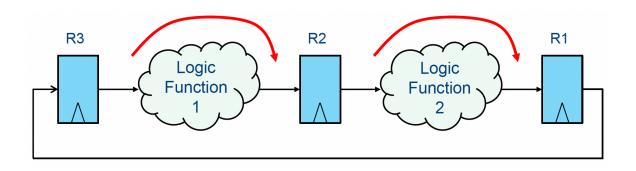

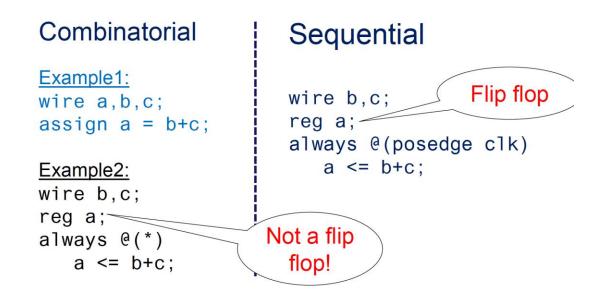

### **Combinational Design vs Sequential Design**

- Combinational design

- Logic computation

- Sequential design

- Logic computation + Memory element

### **Sequential Design**

- Sequential circuits have memory elements and logic computation

- Flip-flops + Combinatorial part

#### **Sequential Design**

- Sequential circuits have memory elements and logic computation

- Flip-flops + Combinatorial part

- Flip-flop outputs change (updated) at only edge of trigger signal

- Clock

- Positive clock edge (posedge)

- Negative clock edge (negedge)

#### **Sequential Design**

- Sequential circuits have memory elements and logic computation

- Flip-flops + Combinatorial part

- Flip-flop outputs change (updated) at only edge of trigger signal

- Clock

- Positive clock edge (posedge)

- Negative clock edge (negedge)

- Reset (optional)

- Dependent to clock (synchronous)

- Independent from clock (asynchronous)

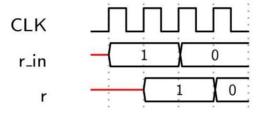

## **Sequential Design – Flip-Flops**

Result is only available after clock's posedge/negedge transition

```

always @ (posedge CLK)

begin

r <= r_in;

end</pre>

```

### **Sequential Design – Flip-Flops**

Result is only available after clock's posedge/negedge transition

```

always @ (posedge CLK)

begin

r <= r_in;

end</pre>

```

#

#### D flip-flop with synchronous reset

```

always @ (posedge CLK)

begin

if(RST)

r <= 0;

else

r <= r_in;

end</pre>

```

#### D flip-flop with asynchronous reset

```

always @ (posedge CLK or posedge RST)

begin

if(RST)

r <= 0;

else

r <= r_in;

end</pre>

```

## **Sequential Design – Reset**

Some sequential elements require a reset signal to initialize the circuit with a known state/value

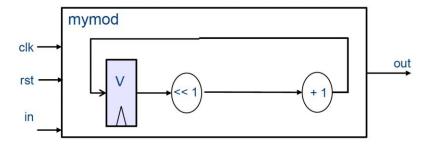

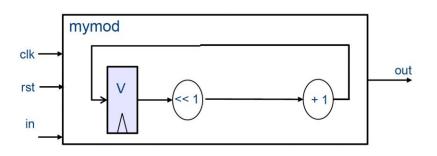

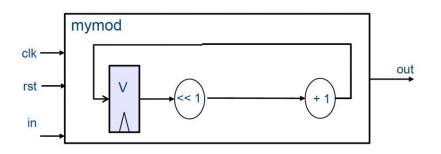

#### **Sequential Design – Reset**

Some sequential elements require a reset signal to initialize the circuit with a known state/value

```

module mymod(clk, rst, in, out);

input clk, rst;

input [7:0] in;

output [7:0] out;

reg[7:0] v;

endmodule

```

#### **Sequential Design – Reset**

Some sequential elements require a reset signal to initialize the circuit with a known state/value

```

module mymod(clk, rst, in, out);

input clk, rst;

input [7:0] in;

output [7:0] out;

reg[7:0] v;

always @(posedge clk)

begin

if (rst)

v <= in;

else

v \le (v \le 1) + 1;

end

assign out = v;

endmodule

```

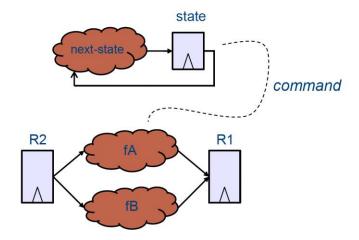

#### **Control Unit (FSM) with Datapath**

Basic idea: Control Unit and datapath exist as separate circuits.

#### Control Unit:

- Controls the data flow

- An easy way to make a control unit: Finite State Machine (FSM)

- Datapath:

- Performs data processing operations

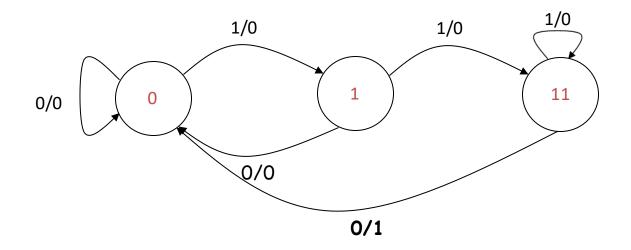

## Design with FSM and Datapath Example – A pattern detection circuit

- A pattern detection circuit

- A circuit takes 1-bit input and outputs "1" when the last 3-bits that it takes are "110". Otherwise, it outputs "0".

### Design with FSM and Datapath Example – A pattern detection circuit

```

module PD(input clk, reset, bit i,

output bit o);

reg [1:0] next state;

reg [1:0] curr state;

reg bit o;

parameter ST 0 = 2'd0,

parameter ST 1 = 2'd1;

parameter ST 11 = 2'd2;

//State register

always@(posedge clk)

begin

if (reset)

curr state <= ST 0;

else

curr state <= next state;</pre>

end

```

#### Design with FSM and Datapath Example – A pattern detection circuit

```

//Next state logic

always@(*) begin

case (curr state)

ST 0 : next state = (bit i == 1) ? ST_1 : ST_0;

ST 1 : next state = (bit i == 1) ? ST_11 : ST_0;

ST 11: next state = (bit i == 1) ? ST 11 : ST 0;

default: next state = ST 0;

end

// output logic

always@(posedge clk) begin

if (reset)

bit o <= 0;

else

bit o <= (curr state == ST 11 && bit i == 0) ? 1 : 0;

end

endmodule

```

# **Verilog Testbench**

- Used to simulate design and test its functional correctness.

- Simulation is much faster than testing/debugging on actual hardware.

#### **Verilog Testbench**

- How to generate a testbench for your combinatorial design module?

- 1. Create a new module for testbench (tb)

- 2. Create a reg for each input of your design in tb

- 3. Create a wire for each output of your design in the

- 4. Create clock (if your design has a clock)

- 5. Instantiate your design in tb

- 6. Connect regs and wires to your design in tb

- 7. Give inputs to your input

- 8. Observe/verify outputs

- Let's look at the pattern detector example.

1. Create a new module for testbench (tb)

```

`timescale 1ns/1ps

module PD tb();

```

```

endmodule

```

2. Create a reg for each input of your design in tb

```

`timescale 1ns/1ps

module PD tb();

reg clk, reset, bit i;

endmodule

```

3. Create a wire for each output of your design in tb

```

`timescale 1ns/1ps

module PD tb();

reg clk, reset, bit i;

wire bit o;

```

```

endmodule

```

4. Create a clock

```

`timescale 1ns/1ps

module PD tb();

reg clk, reset, bit i;

wire bit o;

always #5 clk = ~clk;

```

```

endmodule

```

5+6. Instantiate your design in tb + Connect regs and wires to your design in tb

```

`timescale 1ns/1ps

module PD tb();

reg clk, reset, bit i;

wire bit o;

always #5 clk = \simclk;

PD dut(clk,reset,bit i,bit o);

```

```

endmodule

```

7+8. Give inputs to your design and observe outputs

```

`timescale 1ns/1ps

module PD tb();

reg clk, reset, bit i;

wire bit o;

always #5 clk = \simclk;

PD dut(clk, reset, bit i, bit o);

```

```

initial begin

// initialize all to 0

clk=0; reset=1; bit i=0;

#20; // wait for 20 ns

reset=0;

#10; // wait for 10 ns

bit i=1; #20;

bit i=0; #20;

end

endmodule

```

7+8. Give inputs to your design and observe outputs

```

`timescale 1ns/1ps

module PD tb();

Value

Name

↓ clk

↓ reset

¼ bit i

⊌ bit o

PD dut(clk, reset, bit i, bit o);

```

```

initial begin

// initialize all to 0

clk=0; reset=1; bit i=0;

#20; // wait for 20 ns

reset=0;

#10; // wait for 10 ns

bit i=1; #20;

bit i=0; #20;

end

endmodule

```

#### **Common Mistakes/Bad Practices – Latches**

- Latches easily cause timing problems:

- In simulation: latches give correct results.,

- On hardware: they almost always cause wrong results.

- The tool throws warning when detecting latches in your design.

#### Not Solved! Latches reg b; reg b; always @(\*) always $\theta(*)$ begin begin if (condition) if (condition) $b \le b in1;$ $b \le b in1$ ; else end; b <= b: end;

Example 1:

#### **Common Mistakes/Bad Practices – Latches**

- Latches easily cause timing problems:

- In simulation: latches give correct results.,

- On hardware: they almost always cause wrong results.

- The tool throws warning when detecting latches in your design.

#### Example 1: Solved Latches reg b; reg b; always @(\*) always $\theta(*)$ begin begin if (condition) if (condition) $b \le b in1$ ; b <= b in1: else end; b <= 0; end;

#### **Common Mistakes/Bad Practices – Latches**

- Latches easily cause timing problems:

- In simulation: latches give correct results.,

- On hardware: they almost always cause wrong results.

- The tool throws warning when detecting latches in your design.

#### Example 2:

```

Fixed

Latches

reg a;

reg a;

always \theta(*)

always @(*)

begin

begin

case (condition)

case (condition)

0: a \le a in:

0: a \le a in:

default: a <= 0;

endcase;

endcase;

end;

end:

```

#### **Common Mistakes/Bad Practices – Multi-driven Nets**

Multi-driven nets

```

reg state;

reg [7:0] a,b;

always @(posedge clk)

begin

if (state==0)

a <= 1;

else

a <= 2;

end:

end

always @(posedge clk)

begin

if (state==0)

b <= 1:

else

b <= 2;

a <= 1:

end:

end;

```

Tip: Multiple always blocks simplifies your design.

#### Be careful!

Never assign the same "reg" in two different always blocks.

Why? Always blocks run in parallel.

### **Common Mistakes/Bad Practices – Combinatorial Loops**

Combinatorial loops

wire [7:0] b; assign

$$b = b + 1$$

;

No combinatorial loops between signals in a clock cycle

#### **Common Mistakes/Bad Practices – Mixed Control Unit and Datapath**

Never use the same always block for control unit and datapath

#### **BAD**

```

reg state;

reg [7:0] R1, R2;

always @(posedge clk) begin

state <= state ^ 1;

if (state==0)

R1 <= R2 + 1;

else

R1 <= R2 << 2;

end</pre>

```

#### Advantages:

- Easier to maintain and read code

- Likely to lead to better critical path

- Easier for tool to synthesize

#### GOOD

```

reg state;

reg[7:0] r;

always @(*) begin

if (state==0)

R1 \le R2 + 1;

else

R1 <= R2 << 2;

end

always @(posedge clk)

begin

state <= state ^ 1;

end;

```