# **FPGAs in Space**

Manuel Jedinger

December 15, 2021

## **Example Frame Title**

## • History

- Challenges and Risks

- Political Challenges

- Specialized Hardware

- FPGAs developed for Space

- Remote FPGA Configuration

- Testing Hardware with FLIPPER

- Lessions Learned

# History

- At first only ASIC were used.

- Very Large Scale integration "VLSI"

- 1985 First ASIC from NASA for ground telemtry processing at the Goddard Space Flight Center

- magnitude improvement in performance, cost and size over previous telemetry processing implementations

- VLSI-based system lead to a wide spread usage of ASICs

- Small Explorer missions, Deep Space Network, Hubble Space Telescope

# First real FPGA in Space

- First FPGA was used in the SAMPEX data processing unit (DPU)

- SAMPEX was launched on July 3, 1992 from Vandenberg Air Force Base into a 550 x 675 km orbit.

- Harris 80C85RH

microprocessor

- 12 Actel FPGAs

- 2000 logic gates

- 2.2 cm<sup>2</sup>

- each 102mW power usage

Figure 1: SAMPEX data processing unit

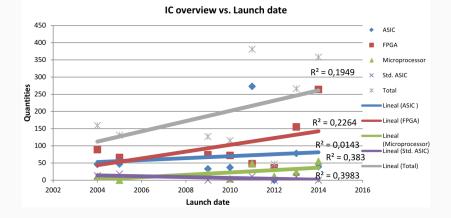

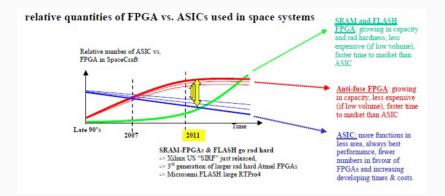

- FPGAs where used more with time

- Advantages

- Increasing integrated circuit design costs

- FPGA offers time-to-market advantage

- Disadvantages

- High volume applications

- Higher power consumption compared to ASIC

# **FPGA** in Space

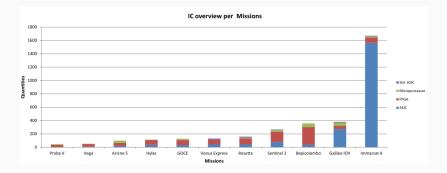

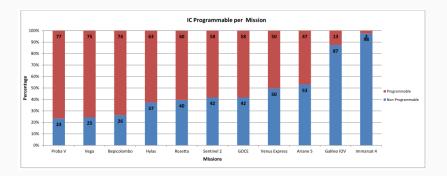

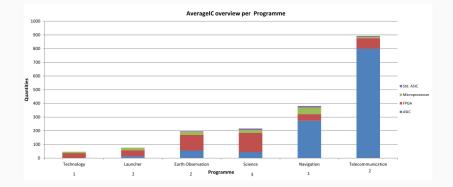

- 2008 Immarsat 4 communication satellite

- 2018 BepiColombo Mercury Planetary Orbiter

Figure 2: Image from tren2012Rog

## **FPGA** in Space

• 2013 Proba V Earth observation for vegetation observation

Figure 3: Image from tren2012Rog

Figure 4: Image from tren2012Rog

Figure 5: Image from tren2012Rog

#### Figure 6: Usage of FPGA and ASIC over time

# **Challenges and Risks**

- Single Event Upsets (SEU)

- Caused by radiation

- Have affects on registers and memory

- therefore they affect the functionality of the combinatorial logic

# Mitigation

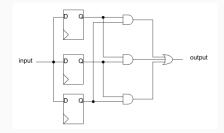

- straight forward mitigation is "Triple Modular Redundancy" for all registers

- does not protect on-chip memory or against multiple upsets

Figure 7: Voting of 3 registers

also works at higher levels: Use 3 FPGAs, reprogram the faulty one

- Use idle cycles in the design for concurrent error detection

- Prototyped using a Xilinx Virtex

- Automatic protection mechanisms for registers and memory in code

- Mechanisms based on Hamming coding and two dimensional parity arrays

- Approach has been demostrated using Altera and Xilinx devices suit2002Sandi

- Using Silicon on insulator (SOI) transistors

- Used for radiation-sensitive applications

- Better protection against SEU/radiation

- Lot of other Hardware based optimizations

- Different memory technologies, directional routing...

# **Political Challenges**

- All major space FPGA suppliers are US companies

- Space parts must be checked by US International Traffic in Arms Regulation (ITAR)

- If technologies are protected Information is restricted to US citizens

- ITAR is an intend to stop American technology falling into enemy hands

- ESA complained that these restrictions complicate project management

# Specialized Hardware - FPGAs developed for Space

- Xilinx offers different product families

- Normal, Dfense Grade and Space Grade

- Space Grade is normally a few generations behind

- Latest Space Grade Xilinx FPGA "Kintex UltraScale" was introduced 2014 for normal usage

- Are used in many satellites

- Iridium Next (US, 66 active satellites)

- Glonass-K (Russian space-based satellite navigation system)

- NovaSAR-S

- Used in research satellites because they are "On-Orbit Reconfigurable"

- 20nm (previous Space-Grade FPGA Virtex-5QV was 64nm)

- 38mb memory

- Lots of communication hardware

- Radiation-Effects Mitigation and Hardness

- Layout of the configuration memory cells is optimized with SEU design rules

- Users can enable build-in tools for more hardness like triple modular redundancy and error detection

- periodic device reconfiguration

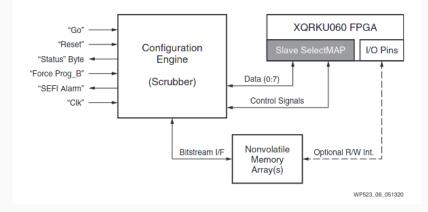

## **RT Kintex UltraScale**

• Own configuration engine for periodic reconfiguration

#### Figure 8: Image from kin2020xil

## **RT Kintex UltraScale**

#### • Radiation Characteristics

| Symbol   | Description                                                                            | Min | Тур    | Max | Units            |

|----------|----------------------------------------------------------------------------------------|-----|--------|-----|------------------|

| TID      | Total Ionized Dose (GEO)                                                               | -   | 100    | 120 | Krad (Si)        |

| SEL      | Single-Event-Latch-Up Immunity                                                         | -   | 80     | -   | MeV-cm2/mg       |

| SEUCRAM  | Single-Event Upset in Configuration RAM (GEO)                                          | -   | 1.0e-8 | -   | Upset/bit/day    |

| SEUBRAM  | Single-Event Upset in Block RAM (GEO)                                                  | -   | 8.5e-9 | -   | Upset/bit/day    |

| SEFICRAM | Single Event Functional Interrupt Orbital Upset<br>Frequency – Configuration RAM (GEO) | -   | 4.5e-4 | -   | Upset/device/day |

#### Figure 9: Image from kin2020xil

## **RT Kintex UltraScale**

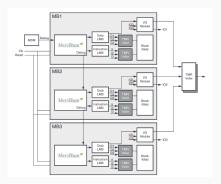

- Can utilize the TMR idea

- Implemented using software IPs (3x 32bit RSIC processors)

Figure 10: Image from kin2020xil

# Specialized Hardware - Remote FPGA Configuration

# CFTP

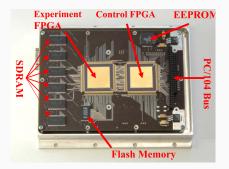

- Configurable Fault Tolerant Processor

- Project from Naval Postgraduate School

- Same FPGA two times, one for experiments

- Allows simple experiments and tests with FPGAs in Space

Figure 11: Image from chal2005sur

# Specialized Hardware - Testing Hardware with FLIPPER

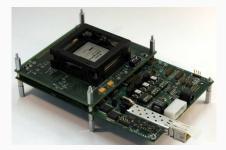

# FLIPPER

- Project founded by ESA

- Emulates fault emulation for SRAM-based FPGA devices

- Acomplished by partial reconfiguration

- Two major releases, latest one with Virtex-5

Figure 12: Flipper with Xilinx Virtex-4, Image from isaf2017Flipper

- Quantitative characterization of design robustness

- Can be used for comparison of design hardening techniques

- Tuning of design redundancy and protection

# **Lessions Learned**

- In a recent satellite project a task force was formed to investigate FPGA desings in critical systems less2002Sandi

- Conclusions:

- Designers are often unaware of how the synthesis tools work

- Little effort had been done to verify that SEU protection were actually implemented

- It is extremely costly to perform a review a long time after the design has been completed

- Poor awareness in spacecraft projects regarding the sheer number of FPGA designs and parts used on spacecrafts

- WIRE Wide-field Infrared Explorer (also Explorer 75 and SMEX-5)

- NASA satellite

- The FPGA on board was a synchronous reset

- Startup time for the oscillator was not taken into consideration

- Default values during startup where not checked

- The telescope cover came off prematurely and the telescope was unusable

### References i

M. Alderighi, M. Uslenghi, S. D'angelo, and M. Fiorini *R&D* experiences on *FPGAs* and astronomical applications at *IASF Milano*. http://sait.oat.ts.astro.it/MmSAI/88/PDF/131.pdf.

Online; accessed 8 December 2021.

- [2] Sandi Habinc Suitability of reprogrammable FPGAs in space applications. http://microelectronics.esa.int/techno/ fpga\_002\_01-0-4.pdf. Online; accessed 9 December 2021.

- [3] Sandi Habinc Lessons Learned from FPGA Developments -Technical Report. http://microelectronics.esa.int/ asic/fpga\_001\_01-0-2.pdf. Online; accessed 8 December 2021.

- [4] Roger Boada Gardenyes Trends and patterns in ASIC and FPGA use in space missions and impact in technology roadmaps of the European Space Agency. https://upcommons.upc.edu/bitstream/handle/2099. 1/17994/RogerBoada-MasterThesis(submission).pdf. Online; accessed 10 December 2021.

- Rash, James L Third International Symposium on Space Mission Operations and Ground Data Systems, part 1. https://ntrs.nasa.gov/citations/19950010764.

Online; accessed 8 December 2021.

- [6] D. J. Mabry, S.J. Hansel, and J.B. Blake The SAMPEX Data Processing Unit. http://www.srl.caltech.edu/sampex/ DataCenter/docs/DPU\_description.pdf. Online; accessed 10 December 2021.

- [7] Xilinx, Inc. RT Kintex UltraScale FPGAs for Ultra High Throughput and High Bandwidth Applications. https: //www.xilinx.com/content/dam/xilinx/support/ documentation/white\_papers/wp523-xqrku060.pdf. Online; accessed 8 December 2021.

[8] Ms. Mindy Surratt, Dr. Herschel H. Loomis, Dr. Alan A. Ross, Dr. Russ Duren Challenges of Remote FPGA Configuration for Space Applications. https://www.researchgate.net/ publication/224624873\_Challenges\_of\_Remote\_FPGA\_ Configuration\_for\_Space\_Applications. Online; accessed 8 December 2021.