# **Modeling Systems**

Chapter 3

## **Modeling Systems**

- 3.1 Transition Systems and Kripke Structures

- 3.2 Nondeterminism and Inputs

- 3.3 First-Order Logic and Symbolic Representations

- 3.4 Boolean Encoding

- 3.5 Modeling Digital Circuits

- 3.6 Modeling Programs

- 3.7 Fairness

## Systems and Correctness

- We consider a broad range of systems

- Hardware (digital circuitry)

- Software

- We want to check that the system is correct

- Meets high-level requirements

- Captured in the form of system properties

## Why Model?

#### **Specification**

States what you want to prove

#### **System**

Abstract away unnecessary details

- How does the OS scheduler work?

- How is the CPU pipeline implememnted?

- What are the voltage levels in the CPU?

#### **But careful!**

- Carelessly implemented CPUs introduce side channels

- Alpha particles may cause bits to flip

- Your formally verified system will fail when hit with a hammer

- ...

#### What is a Model?

- A model is a description of the behavior of the system

- Behavior is

- a set of observations

- as the system evolves its state over time

- We check algorithmically that the model satisfies the properties

- To this end the model...

- must have sufficient detail to prove the property

- but should not be too complex

## **Transition Systems**

- A transition system is a formal model

- Formal models enable formal proof

## **Kripke Structures**

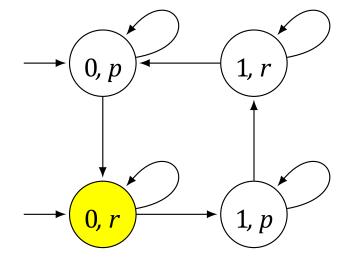

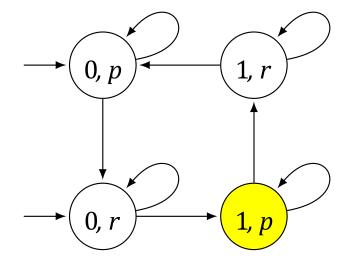

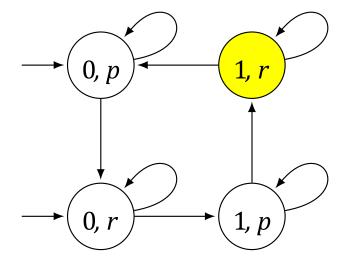

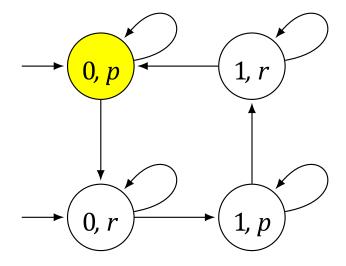

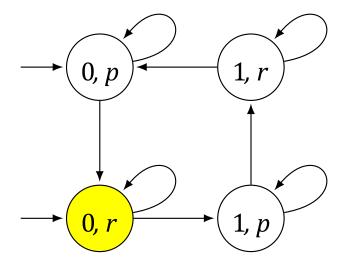

## Inputs

- Inputs are fully under the control of the environment

- We can use nondeterminism to model inputs

- Input: "button pressed" or "button released", controlled by a hand, which is part of the environment

- Output: "light on" or "light off"

- Button is "retractive", it bounces back

- When the light is off, pushing the button turns the light on

- When the light is on, pushing the button turns the light off

light switch "released" = r

light bulb "off" = 0

model of the controller

"pressed" = p

light bulb

"on" = 1

model of the controller

light switch "released" = r

light bulb "on" = 1

model of the controller

light switch "pressed" = p

"off" = 0

model of the controller

model of the controller

## Kripke Structure $M = (S, S_0, R, AP, L)$

- S (finite) set of states

- $S_0 \subseteq S$  set of initial states

- R ⊆ S×S left-total transition relation

- For every  $s \in S$  there exists  $s' \in S$  such that  $(s, s') \in R$

- Left-total implies that every path is infinite

- AP finite set of atomic propositions

- L: S  $\rightarrow$  2<sup>AP</sup> labeling function that associates every state with the atomic propositions true in that state

# First-Order Logic and Symbolic Representations

## **Symbolic Representation**

$$V = \{v_1, \dots, v_n\}$$

system variables  $D_v$  domain of  $v$   $s: V \to \bigcup_{v \in V} D_v$  valuation, state

#### **Example**

## **Symbolic Representation**

$$V = \{v_1, \dots, v_n\}$$

system variables  $D_v$  domain of  $v$   $s: V \to \bigcup_{v \in V} D_v$  valuation, state

#### **Example**

$$V = \{v_1, v_2, v_3\}, D_{v_i} = N$$

State space: **N**<sup>3</sup>

examples of state:  $\{(v_1, 2), (v_2, 3), (v_3, 8)\}$  (short: (2,3,8))

## **Characteristic Functions**

In general, a formula is a set of states.

## **Characteristic Functions**

In general, a formula is a set of states.

$$v_1 = 2 \land v_2 = 3 \land v_3 = 8$$

(2,3,8)

$v_1 = 2 \land v_2 = 3$   $\{(2,3,n_3) \mid n_3 \in N\}$

$v_2 = 3 \land v_3 = v_1 + v_2$   $\{(n_1,3,n_1+3) \mid n_1 \in N\}$

$true$   $N^3$

## **Sets and Formulas**

Formula

$\mathcal{A},\mathcal{B}$

A, B

Set

$A \cup B$

$A \cap B$

$S = D_{v_1} \times \cdots \times D_{v_n}$

$S \setminus A$

#### **Example**

$$v_1 = 2 \land v_2 = 3$$

$v_2 = 3 \land v_3 = v_1 + v_2$

$$\{ (2,3,n_3) \mid n_3 \in \mathbb{N} \}$$

$\{ (n_1,3,n_1+3) \mid n_1 \in \mathbb{N} \}$

•

## **Sets and Formulas**

```

Formula Set \mathcal{A},\mathcal{B} \qquad A,B \mathcal{A}\vee\mathcal{B} \qquad A\cup B \mathcal{A}\wedge\mathcal{B} \qquad A\cap B \mathsf{true} \qquad \mathsf{S}=D_{v_1}\times\cdots\times D_{v_n} \neg\mathcal{A}\wedge\mathcal{B} \qquad \mathsf{S}\setminus A

```

#### **Example**

$$\begin{array}{lll} v_1 = 2 \wedge v_2 = 3 & & \{ (2,3,n_3) \mid n_3 \in \mathbf{N} \} \\ v_2 = 3 \wedge v_3 = v_1 + v_2 & \{ (n_1,3,n_1+3) \mid n_1 \in \mathbf{N} \} \\ v_1 = 2 \wedge v_2 = 3 \wedge v_2 = 3 \wedge v_3 = v_1 + v_2 & \{ (2,3,n_3) \mid n_3 \in \mathbf{N} \} \cup \{ (n_1,3,n_1+3) \mid n_1 \in \mathbf{N} \} \\ v_1 = 2 \wedge v_2 = 3 \vee v_2 = 3 \wedge v_3 = v_1 + v_2 & \{ (2,3,n_3) \mid n_3 \in \mathbf{N} \} \cup \{ (n_1,3,n_1+3) \mid n_1 \in \mathbf{N} \} \end{array}$$

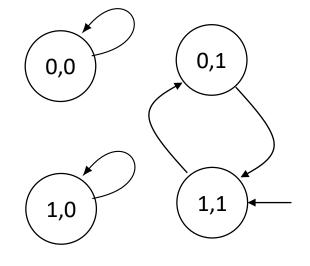

## **Transition Systems**

#### Example

System with variables x, y that range over  $\{0,1\}$ .

Initially, (x, y) = (1,1) and then

$$x := (x + y) \mod 2$$

.

Kripke structure

Initial states:  $S_0(x, y) = x = 1 \land y = 1$

Transitions:  $\mathcal{R}(x, y, x', y') = (x' = (x + y) \mod 2) \land (y' = y)$

## **Transition Systems**

#### Example

System with variables x, y that range over  $\{0,1\}$ . Initially, (x,y) = (1,1) and then  $x := (x + y) \mod 2$ .

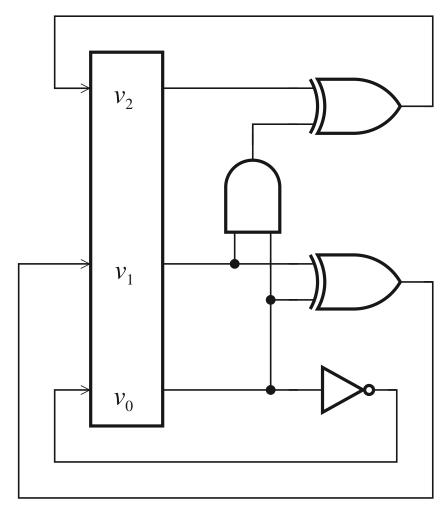

## **Modeling Digital Circuits**

- Inputs are fully under the control of the environment

- We can use nondeterminism to model inputs

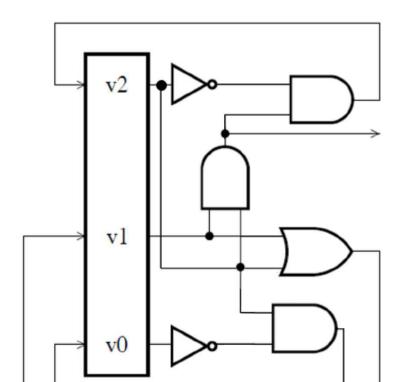

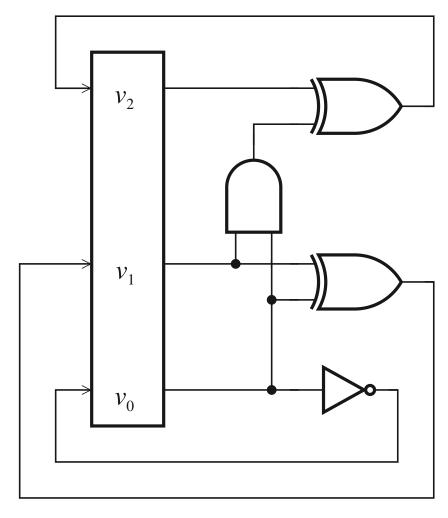

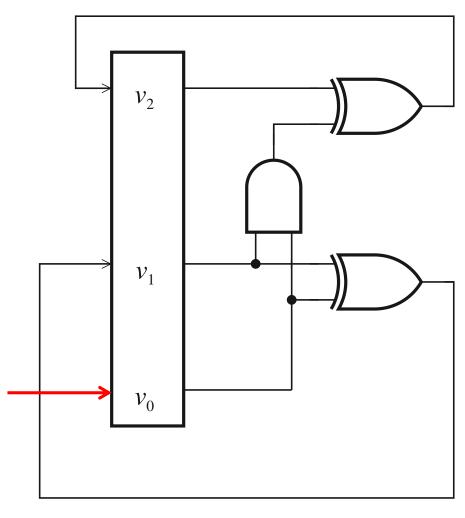

## 3-bit Counter

$$\begin{aligned} \mathcal{R}_0(V,V') &= (v_0' \leftrightarrow \neg v_0) \\ \mathcal{R}_1(V,V') &= (v_1' \leftrightarrow v_0 \oplus v_1) \\ \mathcal{R}_2(V,V') &= \left(v_2' \leftrightarrow v_2 \oplus (v_0 \land v_1)\right) \\ \mathcal{R}(V,V') &= \mathcal{R}_0 \land \mathcal{R}_1 \land \mathcal{R}_2 \end{aligned}$$

## **3-bit Counter**

28

Inputs can be anything - model as nondeterministic

$$\begin{split} \mathcal{R}_0(V,V') &= . \\ \mathcal{R}_1(V,V') &= (v_1' \leftrightarrow v_0 \oplus v_1) \, \mathcal{R}_2(V,V') &= \\ \left(v_2' \leftrightarrow v_2 \oplus (v_0 \wedge v_1)\right) \end{split}$$

## **Inputs**

Inputs can be anything - model as nondeterministic

$$\mathcal{R}_0(V,V') = true$$

no constraints on  $v_1$

$$\mathcal{R}_1(V, V') = (v'_1 \leftrightarrow v_0 \oplus v_1)$$

$$\mathcal{R}_2(V, V') = (v'_2 \leftrightarrow v_2 \oplus (v_0 \land v_1))$$

What does the Kripke structure look like?

## Symbolic Representations

**Hope:** Sets (transition relation, all reachable states) will have small formulas

#### We know

- + size of transition relation ≅ size of circuit, software

- To represent a subset of  $\{1, ..., 2^k\}$  we need  $2^k$  bits in general

We will try to find algorithms that only produce small formulas

## **Asynchronous Systems**

skipped

## **Modeling Software**

#### **Programs**

Consist of

- consecution (;)

- if

- while

- x:=e, skip, wait

- labels ⊥:

Assume every line has a label.

```

Example

P0::

10: while true do

NC0: wait(turn = 0);

CR0: turn := 1

end while

P1::

11: while true do

NC1: wait(turn = 1);

CR1: turn := 0

```

end while

Define

$$same(Y) = \bigwedge_{y \in Y} y = Y'$$

Define

$$C(l, s, l')$$

label of statement statement label of next statement

$$C(l, v \coloneqq e, l') =$$

$$C(l, skip, l') =$$

$$\mathcal{C}(l,(P;l':P'),l'') =$$

Define

$$same(Y) = \bigwedge_{y \in Y} y = Y'$$

Define

$$C(l, s, l')$$

label of statement statement label of next statement

$$C(l, v \coloneqq e, l') = pc = l \land pc' = 'l \land v' = e \land same(V \setminus \{v\}),$$

$$C(l, skip, l') = pc = l \land pc' = 'l \land same(V),$$

$$C(l, (P; l': P'), l'') = C(l, P, l') \lor C(l', P', l''),$$

```

\mathcal{C}(l, \text{if b then } l_1: P1 \text{ else } l_2: P2 \text{ end if, } l') = (pc = l \land b \land pc' = l_1 \land same(V) \lor (pc = l' \land \neg b \land pc' = l_2 \land same(V) \lor \mathcal{C}(l_1, P1, l') \lor \mathcal{C}(l_2, P2, l')

```

```

\mathcal{C}(l, \mathbf{while} \ \mathbf{b} \ \mathbf{do} \ l_1: P1 \ \mathbf{end} \ \mathbf{while}, l') = (pc = l \land b \land pc' = l_1 \land same(V) \lor (pc = l' \land \neg b \land pc' = l' \land same(V) \lor \mathcal{C}(l_1, P1, l)

```

$C(l, if b then l_1: P1 else l_2: P2 end if, l') =$

$C(l, while b do l_1: P1 end while, l') =$

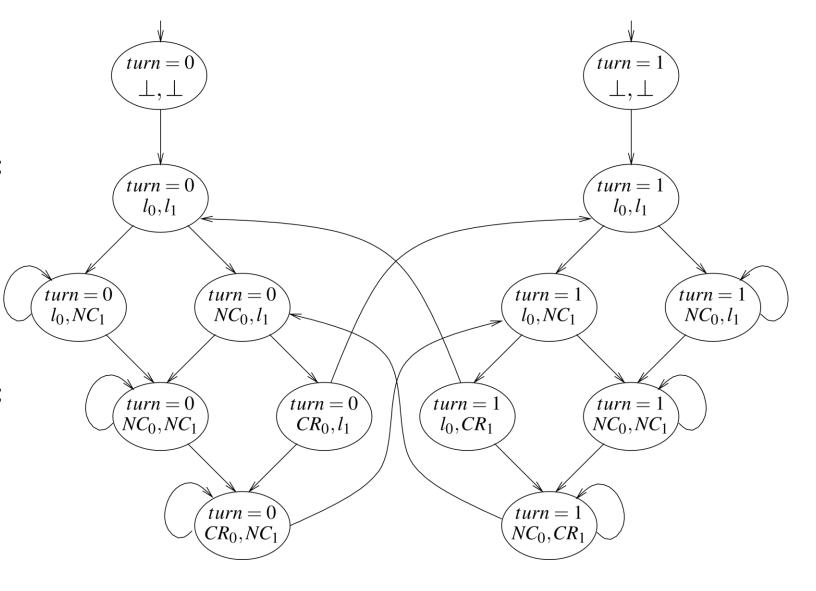

## Concurrency

#### P:: cobegin

```

11:P1 11' ||

12P2 12'

```

#### coend

Three program counters:

- 1. pc for the program that invokes cobegin

- 2.  $pc_1$  for Thread 1

- 3.  $pc_2$  for Thread 2

pc = susp means that the program is not running.

$$\mathcal{C}(l, \mathbf{P}, l') = (pc = l \land pc' = susp \land pc'_1 = l_1 \land pc'_2 = l_2 \land same(V)) \lor$$

$$(pc = susp \land pc_1 = l'_1 \land pc_2 = l'_2 \land pc' = l' \land pc'_1 = susp \land pc'_2 = susp \land same(V)) \lor$$

$$\bigvee_{i=1}^{n} (\mathcal{C}(l_i, P_i, l'_i) \land same(V \backslash V_i) \land same(PC \backslash \{pc_i\})$$

#### Example

P0::

10: while true do

NC0: **wait**(turn = 0);

CR0: turn := 1

#### end while

P1::

l1: while true do

NC1: **wait**(turn = 1);

CR1: turn := 0

end while

## **Fairness**

## **Fairness**

skipped

## Model Checking Homework 1

Deadline: 18.3. 4:00pm

**Sent solution to:** modelchecking@iaik.tugraz.at

Given the following synchronous circuit C.